### VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ BRNO UNIVERSITY OF TECHNOLOGY

FAKULTA INFORMAČNÍCH TECHNOLOGIÍ ÚSTAV INFORMAČNÍCH SYSTÉMŮ

FACULTY OF INFORMATION TECHNOLOGY DEPARTMENT OF INFORMATION SYSTEMS

# REKONFIGUROVATELNÁ ANALÝZA STROJOVÉHO KÓDU

RETARGETABLE ANALYSIS OF MACHINE CODE

DISERTAČNÍ PRÁCE PHD THESIS

AUTOR PRÁCE AUTHOR

VEDOUCÍ PRÁCE SUPERVISOR Ing. JAKUB KŘOUSTEK

Doc. Dr. Ing. DUŠAN KOLÁŘ

BRNO 2014

## Abstrakt

Analýza softwaru je metodologie, jejímž účelem je analyzovat chování daného programu. Jednotlivé metody této analýzy je možné využít i v dalších oborech, jako je zpětné inženýrství, migrace kódu apod. V této práci se zaměříme na analýzu strojového kódu, na zjištění nedostatků existujících metod a na návrh metod nových, které umožní rychlou a přesnou rekonfigurovatelnou analýzu kódu (tj. budou nezávislé na konkrétní cílové platformě). Zkoumány budou dva typy analýz – dynamická (tj. analýza za běhu aplikace) a statická (tj. analýza aplikace bez jejího spuštění). Přínos této práce v rámci dynamické analýzy je realizován jako rekonfigurovatelný ladicí nástroj a dále jako dva typy tzv. rekonfigurovatelného translátovaného simulátoru. Přínos v rámci statické analýzy spočívá v navržení a implementování rekonfigurovatelného zpětného překladače, který slouží pro transformaci strojového kódu zpět do vysokoúrovňové reprezentace. Všechny tyto nástroje jsou založeny na nových metodách navržených autorem této práce. Na základě experimentálních výsledků a ohlasů od uživatelů je možné usuzovat, že tyto nástroje jsou plně srovnatelné s existujícími (komerčními) nástroji a nezřídka dosahují i lepších výsledků.

## Abstract

Program analysis is a computer-science methodology whose task is to analyse the behavior of a given program. The methods of program analysis can also be used in other methodologies such as reverse engineering, re-engineering, code migration, etc. In this thesis, we focus on program analysis of a machine-code and we address the limitations of a nowadays approaches by proposing novel methods of a fast and accurate retargetable analysis (i.e. they are designed to be independent of a particular target platform). We focus on two types of analysis — dynamic analysis (i.e. run-time analysis) and static analysis (i.e. analysing application without its execution). The contribution of this thesis within the dynamic analysis lays in the extension and enhancement of existing methods and their implementation as a retargetable debugger and two types of a retargetable translated simulator. Within the static analysis, we present a concept and implementation of a retargetable decompiler that performs a program transformation from a machine code into a human-readable form of representation. All of these tools are based on several novel methods defined by the author. According to our experimental results and users feed-back, all of the proposed tools are at least fully competitive to existing solutions, while outperforming these solutions in several wavs.

### Klíčová slova

strojový kód, analýza kódu, reverzní inženýrství, zpětný překladač, ladicí nástroj, simulátor, zpětný assembler, gramatiky s rozptýleným kontextem, Lissom, jazyky pro popis architektur, ISAC, škodlivý kód.

### Keywords

machine code, code analysis, reverse engineering, decompiler, debugger, simulator, disassembler, scattered context grammars, Lissom, architecture description languages, ISAC, malware.

## Citation

Jakub Křoustek: Retargetable Analysis of Machine Code, PhD thesis, Brno, FIT BUT, 2014

## **Retargetable Analysis of Machine Code**

### **Statement of Originality**

I hereby declare that this thesis is my own work that has been created under the supervision of doc. Dušan Kolář. Several results were achieved in co-operation with Lukáš Ďurfina, Petr Zemek, Peter Matula, Zdeněk Přikryl, Stanislav Židek, my students, and other members of the Lissom project. Where other sources of information have been used, they have been duly acknowledged.

Jakub Křoustek November 17, 2014

### Acknowledgements

I wish to thank Dušan Kolář for the support during his supervision of this work. I also wish to thank all members of the Lissom research project for their help and ceaseless support of my research. Last, but certainly not least, I wish to thank my family and my girlfriend Lenka for their support and patience during my work on this thesis.

© Jakub Křoustek, 2014.

Tato práce vznikla jako školní dílo na Vysokém učení technickém v Brně, Fakultě informačních technologií. Práce je chráněna autorským zákonem a její užití bez udělení oprávnění autorem je nezákonné, s výjimkou zákonem definovaných případů.

# Contents

| Li | st of                     | Figures                                                             | 5                                    |

|----|---------------------------|---------------------------------------------------------------------|--------------------------------------|

| Li | st of                     | Tables                                                              | 9                                    |

| 1  | <b>Intr</b><br>1.1<br>1.2 | roduction<br>Author's Contribution                                  | <b>11</b><br>13<br>14                |

| 2  |                           | liminaries                                                          | 15                                   |

|    | $2.1 \\ 2.2$              | Theory of Formal Languages                                          | $\begin{array}{c} 15\\17\end{array}$ |

| 3  | Foc                       | us of the Thesis                                                    | <b>23</b>                            |

|    | 3.1                       | CPU Architectures Overview                                          | $\frac{23}{24}$                      |

|    |                           | 3.1.2       RISC Architecture         3.1.3       VLIW Architecture | $24 \\ 25$                           |

|    | 3.2                       | Executable-File Formats Overview                                    | $\frac{25}{26}$                      |

|    |                           | 3.2.1 UNIX Executable and Linking Format                            | 26                                   |

|    |                           | 3.2.2 Microsoft Portable Executable and Common Object File Format   | 27                                   |

|    |                           | 3.2.3Other Common Formats3.2.4Comparison of EFFs                    | $28 \\ 28$                           |

|    | 3.3                       | 3.2.4 Comparison of EFFs                                            | $\frac{20}{29}$                      |

|    | 0.0                       | 3.3.1 DWARF                                                         | $\frac{29}{29}$                      |

|    |                           | 3.3.2 PDB                                                           | 30                                   |

|    |                           | 3.3.3 Other Formats                                                 | 30                                   |

| 4  | Ma                        | chine-Code Analysis: State of the Art                               | <b>31</b>                            |

|    | 4.1                       | Compiler and Packer Detectors                                       | 31                                   |

|    | 4.2                       | EFF Parsers and Converters                                          | 32                                   |

|    | 4.3                       | Disassemblers                                                       | 34                                   |

|    | 4.4                       | Machine-Code Decompilers                                            | 35                                   |

|    | 4.5                       | Debuggers                                                           | 39                                   |

|    | 4.6                       | Tools for Simulation, Emulation, and Instrumentation                | 42                                   |

|    | 4.7                       | Lissom Project                                                      | 44                                   |

|    |                           | 4.7.1 ISAC Language                                                 | 46                                   |

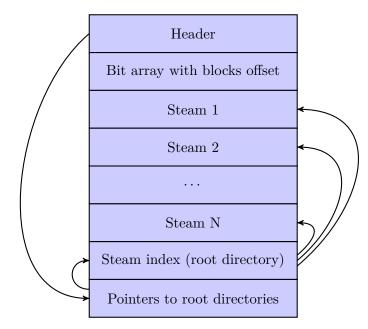

|    |                           | 4.7.2 Lissom Object File Format                                     | 48                                   |

|    |                           | 4.7.3 Toolchain                                                     | 48                                   |

| 5 | Ret | argeta                                        | ble Dynamic Analysis                                     | 53           |

|---|-----|-----------------------------------------------|----------------------------------------------------------|--------------|

|   | 5.1 | Obtair                                        | ing and Processing Debugging Information                 | 54           |

|   |     | 5.1.1                                         | DWARF Parsing                                            | 54           |

|   |     | 5.1.2                                         | PDB Parsing                                              | 58           |

|   | 5.2 | Transl                                        | ated Simulator                                           | 60           |

|   |     | 5.2.1                                         | Translated Simulation Overview                           | 62           |

|   |     | 5.2.2                                         | Static Translated Simulation                             | 62           |

|   |     | 5.2.3                                         | Just-In-Time Translated Simulation (JIT)                 | 67           |

|   | 5.3 | Source                                        | -Level Debugger                                          | 69           |

|   |     | 5.3.1                                         | Lissom Three-Layer Architecture                          | 71           |

|   |     | 5.3.2                                         | Obtaining Debugging Information                          | 72           |

|   |     | 5.3.3                                         | Implementation                                           | 74           |

|   |     |                                               |                                                          |              |

| 6 |     | -                                             | ble Static Analysis                                      | 79           |

|   | 6.1 |                                               | ution                                                    | 80           |

|   |     | 6.1.1                                         | Retargetable Decompilation                               | 81           |

|   |     | 6.1.2                                         | Application of Decompilation                             | 81           |

|   | 6.2 |                                               | ew of the Retargetable Decompiler                        | 83           |

|   | 6.3 | Prepro                                        | cessing Phase                                            | 87           |

|   |     | 6.3.1                                         | Compiler and Packer Detection                            | 89           |

|   |     | 6.3.2                                         | Unpacking                                                | 93           |

|   |     | 6.3.3                                         | Executable-File-Format Conversion                        | 95           |

|   |     | 6.3.4                                         | Context-Sensitive Description of Executable-File-Formats | 97           |

|   | 6.4 | Front-                                        | End Phase                                                | 105          |

|   |     | 6.4.1                                         | Debugging and Symbolic Information Exploitation          | 106          |

|   |     | 6.4.2                                         | Statically-Linked-Code Recognition                       | 107          |

|   |     | 6.4.3                                         | Instruction Decoding                                     | 108          |

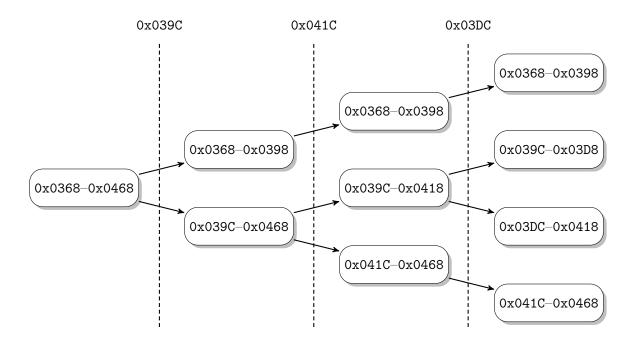

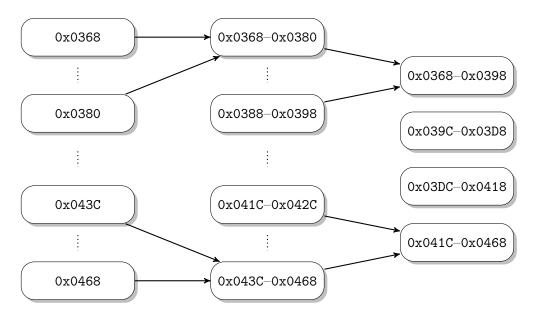

|   |     | 6.4.4                                         | Control-Flow Analysis (CFA)                              | 111          |

|   |     | 6.4.5                                         | Static Code Interpreter                                  | 112          |

|   |     | 6.4.6                                         | Function Detection                                       | 113          |

|   |     | 6.4.7                                         | Data-Flow Analysis (DFA)                                 | 115          |

|   |     | 6.4.8                                         | Other Analyses                                           | 117          |

|   |     | 6.4.9                                         | Outputs Generation                                       | 118          |

|   | 6.5 |                                               | -End Phase                                               | 118          |

|   |     | 6.5.1                                         | Built-in Optimization                                    | 120          |

|   |     | 6.5.2                                         | Instruction-Idiom Analysis                               | 122          |

|   | 6.6 |                                               | End Phase                                                | 130          |

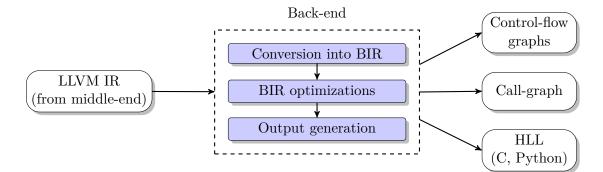

|   | 0.0 | 6.6.1                                         | Back-End Intermediate Representation                     | 131          |

|   |     | 6.6.2                                         | Conversion into BIR                                      | 132          |

|   |     | 6.6.2                                         | BIR Optimizations                                        | $132 \\ 133$ |

|   | 6.7 |                                               | t Generation                                             | $135 \\ 135$ |

|   | 0.1 | 6.7.1                                         | Generation of Control-Flow Graphs                        | $135 \\ 135$ |

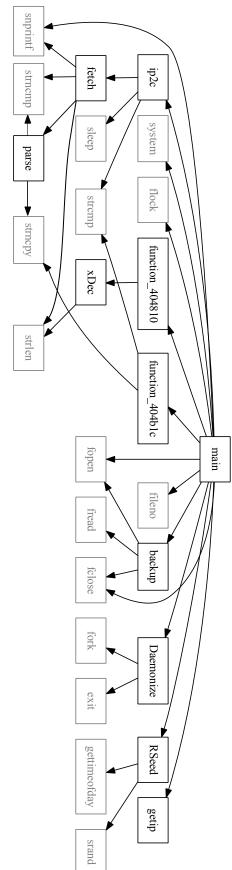

|   |     | 6.7.1<br>6.7.2                                | Generation of Call Graphs                                | $135 \\ 136$ |

|   |     | $\begin{array}{c} 0.7.2 \\ 6.7.3 \end{array}$ |                                                          | $130 \\ 136$ |

|   |     | 0.1.0                                         | Generation of the Output HLL                             | $_{120}$     |

| 7  | Exp        | erime    | ntal Results                                        | 139 |

|----|------------|----------|-----------------------------------------------------|-----|

|    | $7.1^{-1}$ | Transl   | ated Simulation                                     | 140 |

|    | 7.2        | Source   | e-Level Debugging                                   | 142 |

|    | 7.3        | pilation |                                                     |     |

|    |            | 7.3.1    | Compiler and Packer Detection                       |     |

|    |            | 7.3.2    | Function, Argument, and Return Value Reconstruction |     |

|    |            | 7.3.3    | Instruction-Idiom Detection                         |     |

| 8  | Cor        | clusio   | n                                                   | 155 |

|    | 8.1        | Future   | e Work                                              | 156 |

| Bi | ibliog     | graphy   |                                                     | 159 |

| A  | utho       | r's Pul  | olications                                          | 167 |

| Li | st of      | Abbre    | eviations                                           | 171 |

| A  | Dec        | ompila   | ation Results                                       | 173 |

|    | A.1        | Decon    | pilation of Simple Programs                         | 173 |

|    |            |          | pilation of a Real-World Malware                    |     |

|    |            |          | Preprocessing Phase                                 |     |

|    |            | A.2.2    | Front-End Phase                                     | 180 |

|    |            | A.2.3    | Middle-End Phase                                    | 181 |

|    |            | A.2.4    | Back-End Phase                                      | 182 |

|    |            |          | Analysis of the Obtained Results                    |     |

# List of Figures

| 2.1  | Illustration of basic blocks and control-flow graph                     |

|------|-------------------------------------------------------------------------|

|      | 2.1a C source code divided into basic blocks                            |

|      | 2.1b Control-flow graph of the source code                              |

| 2.2  | Example of a call graph                                                 |

|      | 2.2a C source code consisting of four functions                         |

|      | 2.2b Call graph for a given source code                                 |

| 2.3  | Example of def-use chains and use-def chains for variable x             |

| 2.4  | Example of different types of intermediate-code representation          |

|      | 2.4a Three-address code. 20                                             |

|      | 2.4b Static single-assignment form                                      |

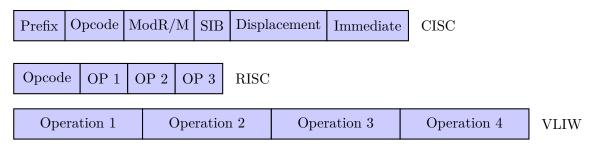

| 3.1  | Example of CISC, RISC, and VLIW instructions                            |

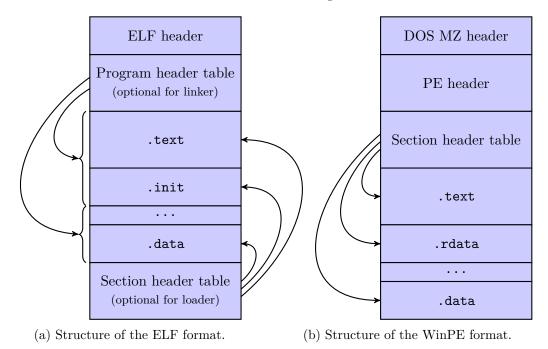

| 3.2  | Structure of the ELF and WinPE executable file formats                  |

|      | 3.2a Structure of the ELF format. 27                                    |

|      | 3.2b Structure of the WinPE format. 27                                  |

|      |                                                                         |

| 4.1  | Example of a BFF-grammar description of the ELF format                  |

| 4.2  | Simplified ISAC ADL model of the MIPS architecture                      |

| 4.3  | Simplified example of the Lisson COFF format                            |

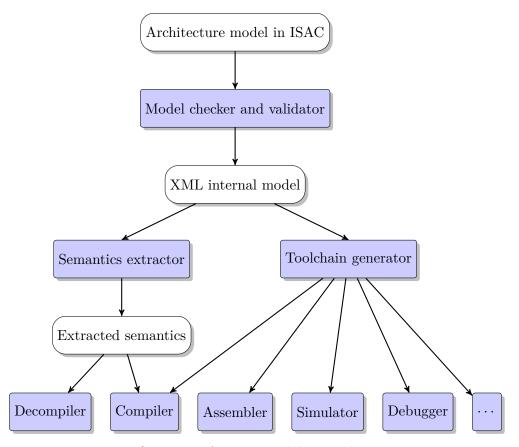

| 4.4  | Overview of Lissom toolchain and its generation                         |

| 4.5  | Example of extracted semantics from an ISAC model                       |

| 5.1  | A simple <i>Hello-world</i> source code in C                            |

| 5.2  | Example of DWARF sections                                               |

| 5.3  | Simplified example of a DWARF debugging information                     |

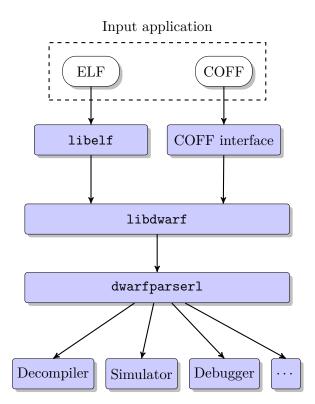

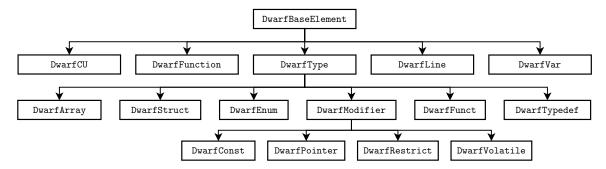

| 5.4  | Structure of the dwarfparserl library                                   |

| 5.5  | Features of the dwarfparserl library 58                                 |

| 5.6  | A simplified structure of a PDB file                                    |

| 5.7  | Example of an ISAC model with two operations                            |

| 5.8  | Example of a two-way coupled finite automaton                           |

| 5.9  | Example of an address-space partitioning in the translated simulator 66 |

| 5.10 | Example of a translated-simulator code                                  |

| 5.11 | Principle of the static translated simulator                            |

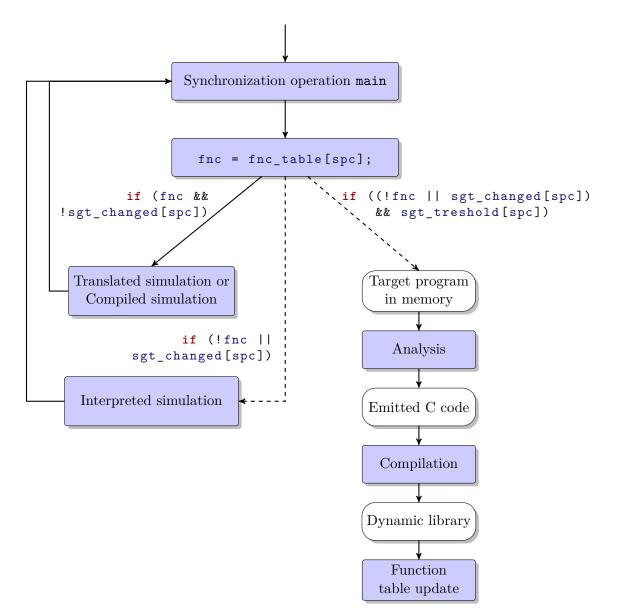

| 5.12 | Principle of the JIT translated simulator                               |

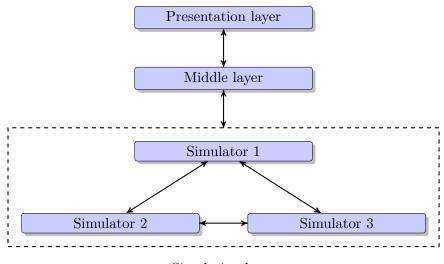

|      | Simplified architecture of the Lissom simulation platform               |

| 5.14 | A snippet of an assembler code with DWARF directives                    |

| 5.15 | An example of a DWARF line information                                  |

| 5.16 | Screenshot of the source-level debugger (lines mapping)                 |

|      |                                                                         |

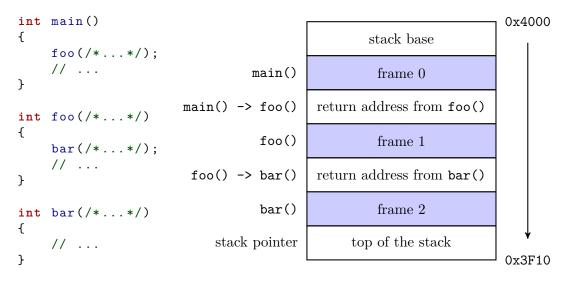

| 5.17 | Stack backtrace illustration within the source-level debugger.         | 77  |

|------|------------------------------------------------------------------------|-----|

|      | 5.17a A simple C application.                                          | 77  |

|      | 5.17b Content of the stack.                                            | 77  |

| 0.1  |                                                                        |     |

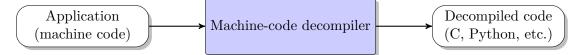

| 6.1  | Illustration of a decompilation process.                               | 80  |

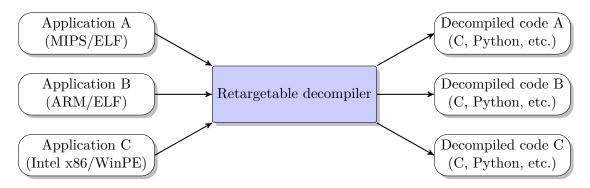

| 6.2  | Illustration of a retargetable-decompilation process                   | 81  |

| 6.3  | Use cases of a decompilation process.                                  | 82  |

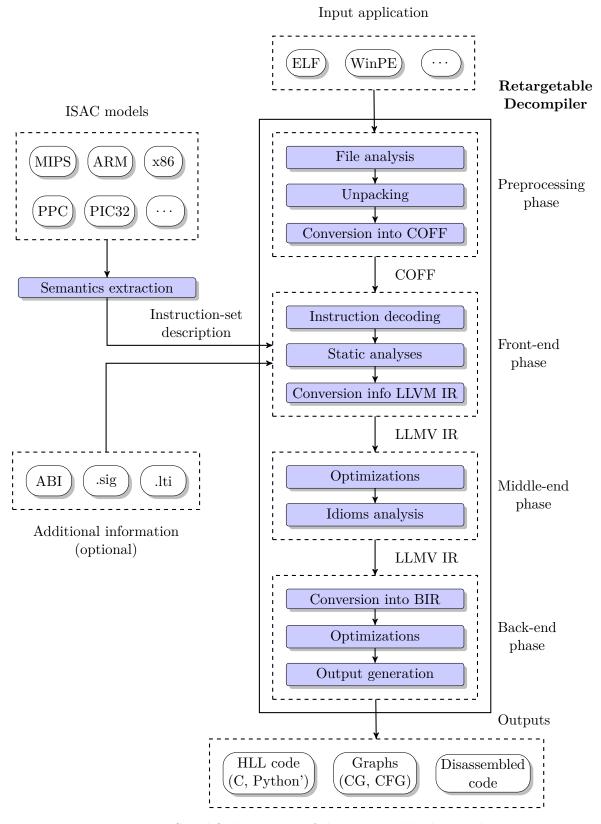

| 6.4  | Simplified structure of the retargetable decompiler.                   | 85  |

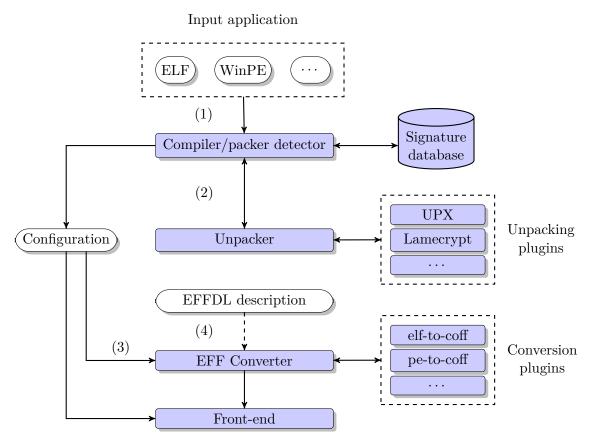

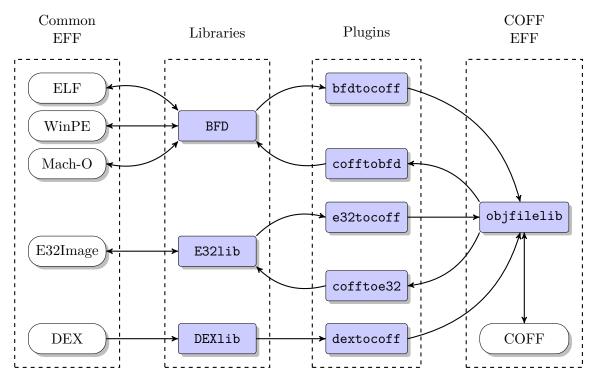

| 6.5  | Concept of the preprocessing phase.                                    | 88  |

| 6.6  | Instruction-idiom example – source code in C                           | 89  |

| 6.7  | Instruction-idiom example – assembly code (GCC 4.0.4)                  | 90  |

| 6.8  | Instruction-idiom example – assembly code (Clang 3.1).                 | 90  |

| 6.9  | Instruction-idiom example – decompiled code (GCC 4.0.4).               | 91  |

|      | Instruction-idiom example – assembly code (GCC 3.4.6)                  | 91  |

| 6.11 | Start-up code for MinGW GCC v4.6 on Intel x86.                         | 92  |

| 6.12 | Example of an advanced signature format for compiler detection         | 92  |

| 6.13 | Example of signatures for the Morphine encryptor.                      | 93  |

| 6.14 | Heuristic detection of the Morphine encryptor v1.2                     | 93  |

| 6.15 | Principle of the plugin-based EFF converter bintran                    | 96  |

| 6.16 | Simplified grammar of the EFFDL                                        | 101 |

| 6.17 | Example of analysers definition in EFFDL.                              | 102 |

| 6.18 | Example of statement types that are usable within analysers in EFFDL   | 102 |

| 6.19 | Usage of attributes and semantic actions within analysers in EFFDL     | 103 |

| 6.20 | Example of different types of analyser calls in EFFDL.                 | 103 |

| 6.21 | A code snippet of an ELF description by using EFFDL.                   | 104 |

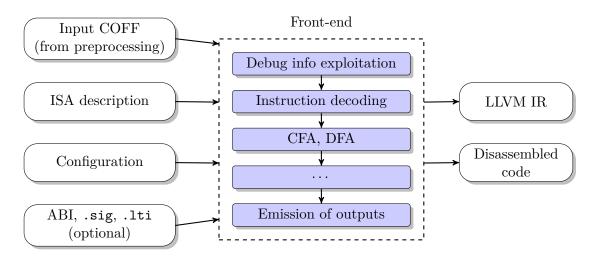

| 6.22 | General structure of the front-end part.                               | 105 |

|      | Decompilation of the factorial function under different circumstances. | 107 |

|      | 6.23a Debugging information.                                           | 107 |

|      | 6.23b Symbolic information.                                            | 107 |

|      | 6.23c Stripped file.                                                   | 107 |

| 6.24 | Assembly code with an indirect branch on the MIPS architecture.        | 112 |

| 6.25 | An example of the top-down function detection.                         | 114 |

| 6.26 | An example of the bottom-up function detection.                        | 115 |

|      | Example of a MIPS ABI description.                                     | 117 |

|      | Example of a generated LLVM IR code for one machine-code instruction.  | 118 |

|      | Example of a disassembled code (Intel x86).                            | 119 |

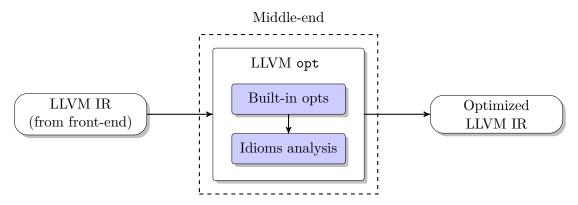

|      | A general view on the middle-end part.                                 | 120 |

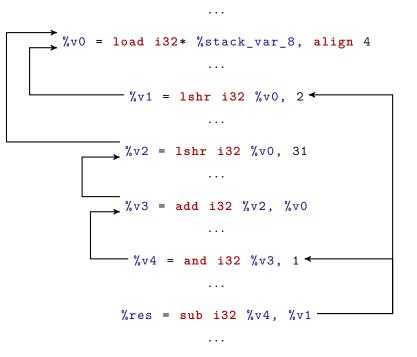

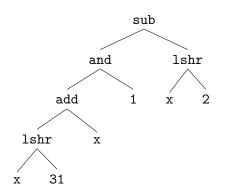

|      | Example of an instruction idiom – usage of the lshr() function.        | 124 |

|      | 6.31a Original C code.                                                 | 124 |

|      | 6.31b Code generated by the GCC compiler                               | 124 |

| 6.32 | Example of a program for decompilation.                                | 126 |

|      | Comparison of a front-end and middle-end LLVM IR code complexity.      | 127 |

|      | 6.33a Front-end part.                                                  | 127 |

|      | 6.33b Middle-end part.                                                 | 127 |

| 6.34 | Example of instruction-idioms inspection in the middle-end part.       | 128 |

|      | Example of an AST used within middle-end phase.                        | 129 |

|      | Example of the bit-clear <b>xor</b> idiom transformation.              | 129 |

|      | 6.36a Optimized form.                                                  | 129 |

|      |                                                                        |     |

|                   | 6.36b De-optimized form.                                                                                                                                                                                                                                                                                                                                                                                                                                    | 129                                                                       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 6.37              | C code example of decompilation with and without the idiom analysis                                                                                                                                                                                                                                                                                                                                                                                         | 130                                                                       |

|                   | 6.37a Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                | 130                                                                       |

|                   | 6.37b Output with idiom analysis enabled.                                                                                                                                                                                                                                                                                                                                                                                                                   | 130                                                                       |

|                   | 6.37c Output with idiom analysis disabled.                                                                                                                                                                                                                                                                                                                                                                                                                  | 130                                                                       |

| 6.38              | General structure of the back-end part.                                                                                                                                                                                                                                                                                                                                                                                                                     | 131                                                                       |

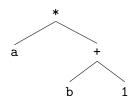

|                   | An LLVM IR representation of <b>return a + 1</b>                                                                                                                                                                                                                                                                                                                                                                                                            | 131                                                                       |

|                   | Representation of the expression <b>a</b> * ( <b>b</b> + 1) in BIR                                                                                                                                                                                                                                                                                                                                                                                          | 132                                                                       |

|                   | Several types of regions defining high-level constructs.                                                                                                                                                                                                                                                                                                                                                                                                    | 132                                                                       |

|                   | Example of a generated control-flow graph.                                                                                                                                                                                                                                                                                                                                                                                                                  | 135                                                                       |

|                   | Example of a generated call graph.                                                                                                                                                                                                                                                                                                                                                                                                                          | 136                                                                       |

|                   | Example of a decompiled Python-like code.                                                                                                                                                                                                                                                                                                                                                                                                                   | 137                                                                       |

|                   | Example of a decompiled C code                                                                                                                                                                                                                                                                                                                                                                                                                              | 137                                                                       |

| 0.10              |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 101                                                                       |

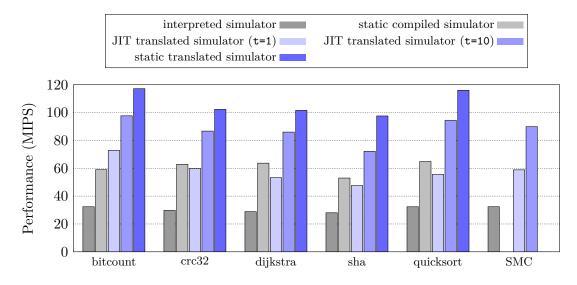

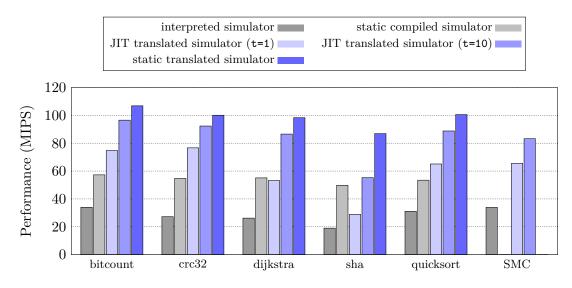

| 7.1               | Performance comparison of all simulator types (MIPS architecture).                                                                                                                                                                                                                                                                                                                                                                                          | 141                                                                       |

| 7.2               | Performance comparison of all simulator types (VEX architecture).                                                                                                                                                                                                                                                                                                                                                                                           | 141                                                                       |

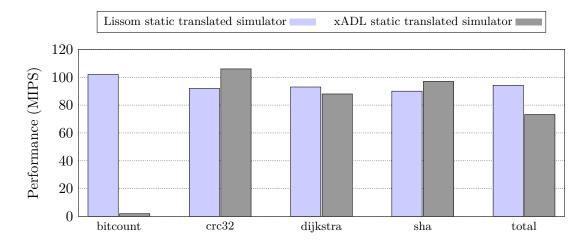

| 7.3               | Performance comparison between Lisson and xADL translated simulators.                                                                                                                                                                                                                                                                                                                                                                                       | 143                                                                       |

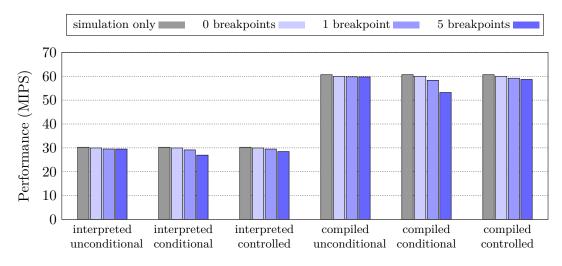

| 7.4               | Simulator speeds of MIPS processor in different debugging scenarios.                                                                                                                                                                                                                                                                                                                                                                                        | 144                                                                       |

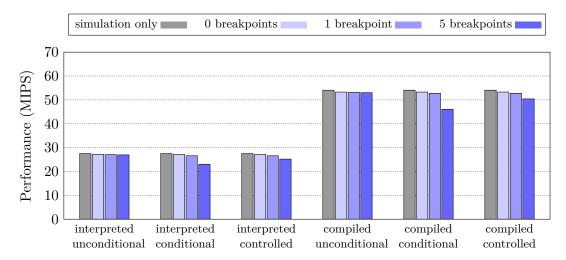

| 7.5               | Simulator speeds of VEX processor in different debugging scenarios.                                                                                                                                                                                                                                                                                                                                                                                         | 144                                                                       |

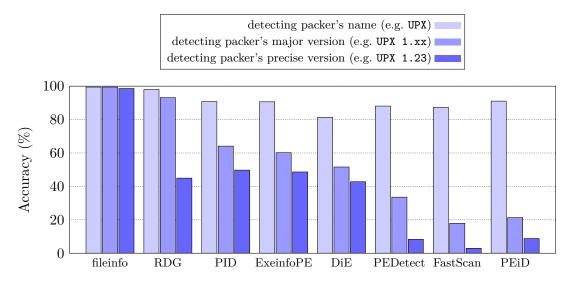

| 7.6               | Comparison of packer-detection accuracy.                                                                                                                                                                                                                                                                                                                                                                                                                    | 146                                                                       |

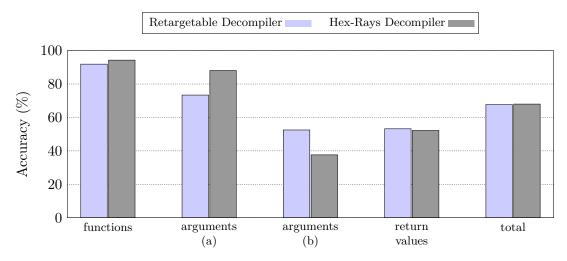

| 7.7               | Total accuracy of function, argument, and return value reconstruction.                                                                                                                                                                                                                                                                                                                                                                                      | 151                                                                       |

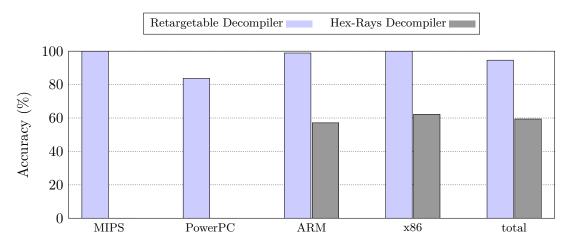

| 7.8               | Accuracy of instruction-idioms detection and code reconstruction.                                                                                                                                                                                                                                                                                                                                                                                           | 154                                                                       |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |

| A.1               | Decompilation of the Ackermann function                                                                                                                                                                                                                                                                                                                                                                                                                     | 174                                                                       |

|                   | A.1a Original code                                                                                                                                                                                                                                                                                                                                                                                                                                          | 174                                                                       |

|                   | A.1b Decompiled code                                                                                                                                                                                                                                                                                                                                                                                                                                        | 174                                                                       |

| A.2               | Decompilation of the factorial function.                                                                                                                                                                                                                                                                                                                                                                                                                    | 175                                                                       |

|                   | A.2a Original code                                                                                                                                                                                                                                                                                                                                                                                                                                          | 175                                                                       |

|                   | A.2b Decompiled code                                                                                                                                                                                                                                                                                                                                                                                                                                        | 175                                                                       |

| A.3               | Decompilation of the Fibonacci function.                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 70                                                                      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 176                                                                       |

|                   | A.3a Original code                                                                                                                                                                                                                                                                                                                                                                                                                                          | 176                                                                       |

|                   | A.3aOriginal code.A.3bDecompiled code.                                                                                                                                                                                                                                                                                                                                                                                                                      | $\begin{array}{c} 176\\ 176 \end{array}$                                  |

| A.4               | A.3aOriginal code.A.3bDecompiled code.Decompilation of the greatest-common-divisor function.                                                                                                                                                                                                                                                                                                                                                                | 176<br>176<br>177                                                         |

| A.4               | A.3aOriginal code.A.3bDecompiled code.                                                                                                                                                                                                                                                                                                                                                                                                                      | $\begin{array}{c} 176\\ 176 \end{array}$                                  |

| A.4               | A.3aOriginal code.A.3bDecompiled code.Decompilation of the greatest-common-divisor function.A.4aOriginal code.A.4bDecompiled code.                                                                                                                                                                                                                                                                                                                          | 176<br>176<br>177                                                         |

| A.4<br>A.5        | A.3aOriginal code.A.3bDecompiled code.Decompilation of the greatest-common-divisor function.A.4aOriginal code.                                                                                                                                                                                                                                                                                                                                              | 176<br>176<br>177<br>177                                                  |

|                   | A.3aOriginal code.A.3bDecompiled code.Decompilation of the greatest-common-divisor function.A.4aOriginal code.A.4bDecompiled code.                                                                                                                                                                                                                                                                                                                          | 176<br>176<br>177<br>177<br>177                                           |

|                   | A.3aOriginal code.A.3bDecompiled code.Decompilation of the greatest-common-divisor function.A.4aOriginal code.A.4bDecompiled code.Decompilation of the instruction idioms.                                                                                                                                                                                                                                                                                  | 176<br>176<br>177<br>177<br>177<br>178                                    |

|                   | A.3aOriginal code.A.3bDecompiled code.Decompilation of the greatest-common-divisor function.A.4aOriginal code.A.4bDecompiled code.Decompilation of the instruction idioms.A.5aOriginal code.                                                                                                                                                                                                                                                                | 176<br>176<br>177<br>177<br>177<br>178<br>178<br>178                      |

| A.5               | A.3aOriginal code.A.3bDecompiled code.Decompilation of the greatest-common-divisor function.A.4aOriginal code.A.4bDecompiled code.Decompilation of the instruction idioms.A.5aOriginal code.A.5bDecompiled code.                                                                                                                                                                                                                                            | 176<br>176<br>177<br>177<br>177<br>178<br>178                             |

| A.5<br>A.6        | A.3aOriginal code.A.3bDecompiled code.Decompilation of the greatest-common-divisor function.A.4aOriginal code.A.4bDecompiled code.Decompilation of the instruction idioms.A.5aOriginal code.A.5bDecompiled code.Psyb0t entry-point instructions.                                                                                                                                                                                                            | 176<br>176<br>177<br>177<br>177<br>178<br>178<br>178<br>178               |

| A.5<br>A.6<br>A.7 | A.3aOriginal code.A.3bDecompiled code.Decompilation of the greatest-common-divisor function.A.4aOriginal code.A.4bDecompiled code.Decompilation of the instruction idioms.A.5aOriginal code.A.5bDecompiled code.A.5bDecompiled code.A.5bDecompiled code.A.5bDecompiled code.A.5bDecompiled code.A.5bDecompiled code.A.5bDecompiled code.A.5bDecompiled code.Psyb0t entry-point instructions.A block generated by the front-end for the instruction jalr t9. | 176<br>177<br>177<br>177<br>178<br>178<br>178<br>178<br>178<br>179<br>181 |

# List of Tables

| 3.1  | A comparison of common EFFs                                            | 29  |

|------|------------------------------------------------------------------------|-----|

| 4.1  | Overview of features and tests of existing machine-code decompilers    | 40  |

| 4.2  | Overview of simulator types within the ADL-based projects              | 45  |

| 6.1  | Overview of heuristics focused on the name and order of sections       | 94  |

| 6.2  | Complexity of several existing EFF parsing libraries.                  | 98  |

| 6.3  | Complexity of Lissom project EFF-conversion plugins.                   | 98  |

| 6.4  | Shortened list of instruction idioms found in compilers                | 125 |

| 7.1  | Complexity of the referred ISAC models in term of code lines           | 140 |

| 7.2  | Times needed for simulator creation (in seconds)                       | 142 |

| 7.3  | Overview of existing compiler/packer detection tools                   | 145 |

| 7.4  | Comparison of Morphine-encryptor detection (in percents).              | 147 |

| 7.5  | Comparison of ELF compilers and packers detection (in percents).       | 147 |

| 7.6  | Accuracy of function detection and reconstruction.                     | 149 |

| 7.7  | Accuracy of arguments reconstruction (no data types)                   | 150 |

| 7.8  | Accuracy of arguments reconstruction (with data types)                 | 150 |

| 7.9  | Accuracy of return-values reconstruction.                              | 151 |

| 7.10 | Number of successfully reconstructed instruction idioms (in percents). | 153 |

| A.1  | Shortened list of functions extracted from symbols.                    | 181 |

| A.2  | Statistics about decompiler output for psyb0t                          | 186 |

# Chapter 1

# Introduction

"Truth can only be found in one place: the code. Only the code can truly tell you what it does."

Robert C. Martin

*Program analysis* is a computer-science methodology, whose task is to analyse the behavior of a given program [62]. By using various methods of program analysis, it is not only possible to understand program behavior, but it can also help with detection and removal of program flaws (i.e. *debugging*<sup>1</sup>), optimization of program execution, program verification, etc. These methods are also used in other methodologies such as reverse engineering, re-engineering, program comprehension, code migration, and many others.

The analysed program can be stored in one of the following forms<sup>2</sup> — source code, bytecode, or machine code. In compiler terminology, the source-code form is the original program form written in a particular programming language. The bytecode and machinecode forms are binary representations of the source code created by a compiler. Code representation in the last two formats is not textual (unlike a source code), but it is in a binary form containing machine instructions. Bytecode is usually interpreted in a particular virtual machine (VM) while machine code is executed on a target processor architecture.

The vast majority of the existing methods of program analysis is related to the sourcecode form. Roughly speaking, analysis of the source code is easier than the others because it is more or less platform independent and all the information necessary for analysis is available within the source code. The source-code representation contains complete behavioral description of the program including details like variable names or user comments. These methods of source-code analysis are well described in literature, e.g. formal verification [56, 73, 90], program slicing [97], or abstract interpretation [95]. They are used in all aspects of software engineering like static error checking, unit testing, debugging, etc.

The bytecode format is employed only in a fraction of architectures, almost always in virtual machines, e.g. Java VM or Android Dalvik VM. For this reason, methods of bytecode analysis are not so common. The important fact about bytecode program representation is that there is only a minor information loss during compilation from source-code into the

<sup>&</sup>lt;sup>1</sup>The term *debugging* denotes "methodology of finding, isolating, and removing defects (bugs) from software programs", according to [77].

$<sup>^{2}</sup>$ There are also other forms of code representation (e.g. object code); however, those are rarely used for program analysis [82].

bytecode [63, 64], e.g. removal of comments and code formatting. Therefore, it is often possible to apply the same program-analysis methods as in the source-code case. Furthermore, the decompilation from bytecode back into the original language is also plausible with only a small effort, see [63] for details.

The term *decompilation* refers to a reverse process to compilation, i.e. translation from an executable-code representation back into the source code. With a few exceptions, we will only use this term for translation from the executable machine-code files into a high-level language (HLL) form in this thesis.

Finally, the machine-code program representation is used in all types of electronic devices around us (personal computers, smart phones, automation, car industry, etc.). Sometimes, it is even used for program acceleration in virtual machines, e.g. Java Native Interface (JNI) in Dalvik VM.

Machine code is almost always created by compilers that use several levels of optimizations. The major difference to the previous types of code representation is that the machine-code representation lacks a significant amount of information. Compilers transform the original program to a different form in order to produce a fast and compact code for a particular target architecture. There are dozens of existing optimization techniques used for this task, e.g. dead-code elimination, tail-call optimization, usage of instruction idioms [1,96]. Furthermore, compilers usually remove any information that is not necessary for execution (e.g. information about original functions that were inlined, information about user-defined data types). Therefore, program analysis of these files is more difficult because it is necessary to reconstruct all the missing information and to deal with a highly-optimized code that is dissimilar to its original form.

At present, we can find several existing techniques and tools for analysis of machine code, like disassemblers, dumpers, or debuggers [13, 20, 80]. They differ in a level of presented information about the analysed program. For example, a disassembler only transforms the machine code into assembly code that is still hardly readable for most analysts. Moreover, most of these tools are limited to a particular target architecture (mostly Intel x86) and they do not support the others. In other words, they are not *retargetable*. This is unfortunate because some architectures are not covered by these tools and program analysis has to be done manually by user.

In this thesis, we address the limitations of present day methods of machine-code analysis and we propose several new methods that are focused on a fast and accurate retargetable analysis. These methods are designed to be independent of a particular target platform, i.e. a combination of a target architecture, file format, and used compiler. We focus on two types of analysis — *dynamic analysis* and *static analysis*.

Dynamic analysis executes the application and analyses its behavior during its run-time. The execution can be done either directly on the target architecture (e.g. remote debugging) or via simulation or emulation. Profilers, simulators, and debuggers are the most common tools within this category.

Static machine-code analysis examines applications without their execution and it is usually focused on program transformation from machine code into a human-readable form of representation. The most common tools are disassemblers that produce assembly code and the more modern decompilers producing an HLL code (C, Java, etc.). Static analysis can also perform control-flow and data-flow checking, see [41] for more details.

Within the dynamic analysis, the contribution of this thesis lays in the extension and enhancement of existing methods and their implementation as two types of a *retargetable translated simulator* and a *retargetable debugger*. In order to enhance existing static-analysis methods, we implemented a *retargetable decompiler*. This tool is based on several novel methods defined by the author.

As an application of these tools, we should mention a high-speed simulation (or emulation/instrumentation) of executable files for new ASIP chips, debugging of a highlyoptimized code, or deep analysis of malicious code (malware). We successfully validated our approaches via implementation of proposed methods and their testing on real-world examples within the Lissom<sup>3</sup> project at Brno University of Technology.

### **1.1** Author's Contribution

In particular, the main author's contribution is as follows:

- ISAC language extensions and architectures modeling In order to support retargetability of the designed tools, the ISAC architecture-description language (ADL) [52] is used for description of target architectures. Afterwards, the ISAC models are used during automatic generation of tools. However, it was necessary to make several enhancements of ISAC language constructions. For this reason, the author added constructions for a description of instruction decoders, modeling of multiple instruction sets, support of less common architectures (e.g. VLIW and its instruction encoding and compression) [121]. Furthermore, the author created (or enhanced) several ISAC models of existing architectures (e.g. VEX, MIPS, ARM).

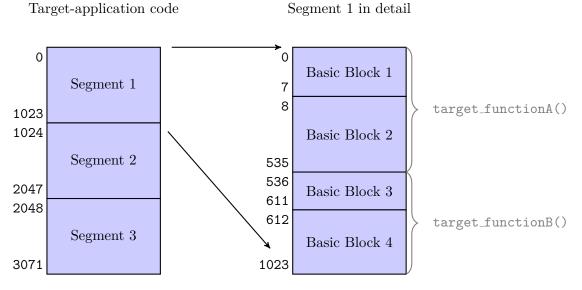

- Exploitation of debugging information Because of a massive lack of information stored in analysed executable files, it is necessary to use every source of available information. One of such sources is debugging information. The author designed an approach for detection, extraction, and representation of debugging information. At present, the two most common formats are supported DWARF and PDB. He also utilized this approach in the following tools. Debugging information is used within the translated simulator for detection of basic blocks [117]. The retargetable debugger uses this information for source-level debugging [113] and the retargetable decompiler exploits it for generation of a more readable code [109]. Furthermore, the extracted information about functions is also used within the profiler for the C language [72]; however, this tool has been created without the author's contribution.

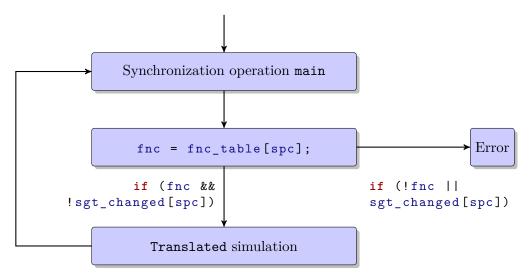

- Static Translated Simulator and Just-In-Time Translated Simulator The author participated in design, implementation, and testing of these tools for a high-speed simulation of applications for target architectures. This work extends the previous work of Zdeněk Přikryl in the field of interpreted [71] and compiled simulators [70]. The newly designed methods lack a simulation of processor microarchitecture; on the other hand, they provide higher simulation speeds. Two versions of this simulator have been designed static [119] and just-in-time translated simulator [118].

- Retargetable Source-level Debugger One of the most common tools for machine-code analysis is a debugger. This tool can basically operate on two levels of abstraction *instruction-level* and *source-level*. The former one is more low-level and it operates on a level of machine instructions, registers, memory cells, etc. Basically, it is only able to investigate the state of the hardware resources during debugging, but it is

<sup>&</sup>lt;sup>3</sup>http://www.fit.vutbr.cz/research/groups/lissom/

mostly unusable for analysis of the original application on its source level. This type of debugger has been already done by other members of the Lissom project. The author created the second level (i.e. support of source-level debugging) on the top of the existing debugger. The source-level debugger supports the retargetable analysis on the source-level with all the previously mentioned features [120]. This extension is used for debugging of applications generated by the Lissom C compiler. The author also contributed with modifications of the compiler toolchain to allow generation of a proper debugging information.

• Retargetable Decompiler – The last tool mentioned in this thesis is a retargetable decompiler. It serves for a static, platform-independent analysis of machine code. Its complexity is much higher than in the previous tools. For this reason, the author designed this tool as a complete toolchain containing multiple applications that are interconnected via scripts [102, 103]. We can divide these applications in the following phases — preprocessing, front-end, middle-end, and back-end. The author participated in design and implementation of most of the methods used within these phases, e.g. detection of originally used compiler/packer [108], unpacking [123], executable-file format conversion [105, 110] (preprocessing phase), exploitation of debugging information [109], instruction decoding [132–134], control-flow and data-flow analysis [131, 135], function detection [128-130] (front-end phase), and instructionidiom reconstruction [111,112] (middle-end phase). The author also contributed during testing of this tool on real-world malware samples [124, 126, 127]. Finally, the author also defined a new formalism scattered context grammar with priority function [114, 115] (and proved its generative power [116]) that can be used for uniform parsing of input binary executable files within the preprocessing phase [107].

Contrariwise, the author has only a very limited contribution in the design of methods used within the back-end phase and no contribution in their implementation as well as in several other methods used within the front-end phase, e.g. elimination of staticallylinked code, data-type recovery, and detection of similarity between two files.

### 1.2 Chapter Survey

The thesis is organized as follows. Firstly, Chapter 2 gives preliminaries and basic definitions, including used notation. These definitions are fundamental for methods presented in Chapters 5 and 6.

The focus of this thesis is specified in Chapter 3. Within this chapter, we briefly describe architectures, file formats, and other standards that we focus on within our methods of machine-code analysis. Afterwards, Chapter 4 discusses the state of the art of machine-code analysis methods, such as related approaches, projects, and tools. Then, in Chapter 5, we present our own methods of dynamic machine-code analysis and their implementation — two different types of translated simulator and the source-level debugger. Afterwards, in Chapter 6, the retargetable decompiler is presented in detail. Experimental results related to these tools are given in Chapter 7. In the conclusion of this work, given in Chapter 8, obtained results are summarized, several final remarks are made, and possible further research is discussed. It also states several open problems closely related to this work. Finally, we present the capabilities of the proposed retargetable decompiler on several examples in Appendix A as well as a case study of malware decompilation by using this tool.

## Chapter 2

# Preliminaries

"In theory, there is no difference between theory and practice. In practice, there is."

Johannes L. A. van de Snepscheut

In this chapter, we present the terminology, notation, and fundamental definitions of the formal language theory and compiler design used in this thesis. The reader is assumed to have basic knowledge of these topics.

Section 2.1 is related to the formal language theory, such as grammars, languages, and their generative power. We pay special attention to scattered context grammars that are often referenced in the latter text. More details about this formalism can be found in [27, 55]. Afterwards, in Section 2.2, we review the terminology used within the area of compiler design, such as basic blocks, control-flow graph, etc. See [1, 60] for further reference. This chapter is based on [35, 54, 69, 78, 79].

### 2.1 Theory of Formal Languages

**Definition 1.** For an alphabet  $V, V^*$  denotes the free monoid generated by V under the operation of concatenation, with the unit element  $\varepsilon$ . Set  $V^+ = V^* - \{\varepsilon\}$ . For  $w \in V^*$ , |w| denotes the length of w.

**Definition 2.** A phrase-structure grammar is a quadruple G = (V, T, P, S), where

- V is a total alphabet;

- $T \subset V$  is a finite set of *terminal symbols* (*terminals*);

- $S \in V T$  is the start symbol of G;

- P is a finite set of productions (rules)  $p = x \rightarrow y, x \in V^*(V T)V^*, y \in V^*$ .

The symbols in V - T are referred to as nonterminal symbols (nonterminals). We set lhs(p) = x and rhs(p) = y, which represents the left-hand side and the right-hand side of the production p, respectively. If  $rhs(p) = \varepsilon$ , p is called *erasing production* ( $\varepsilon$ -rule).

**Definition 3.** Let G = (V, T, P, S) be a phrase-structure grammar,  $y = w_1 \alpha w_2$ ,  $z = w_1 \beta w_2$ ,  $y, z \in V^*$ ,  $p = \alpha \rightarrow \beta \in P$ . Then y directly derives z in the G according to the

production  $p, y \Rightarrow_G z [p]$  (or simply  $y \Rightarrow_G z$ ). Let  $\Rightarrow_G^+$  and  $\Rightarrow_G^*$  denote the *transitive* and the *reflexive-transitive closure* of  $\Rightarrow_G$ , respectively. To express that G makes the *derivation* from u to v by using the sequence of productions  $p_1, p_2, \ldots, p_n \in P$ , we write  $u \Rightarrow_G^* v [p_1 p_2 \ldots p_n]$  (or  $u \Rightarrow_G^+ v [p_1 p_2 \ldots p_n]$  to emphasize that the sequence is non-empty).

**Definition 4.** The *language* generated by G is denoted by L(G) and defined as  $L(G) = \{w : w \in T^*, S \Rightarrow_G^* w\}$ . A recursively-enumerable language (RE language) is a language generated by a phrase-structure grammar. The family of recursively-enumerable languages is denoted by  $\mathcal{L}(RE)$ .

**Definition 5.** A context-sensitive grammar (CS grammar) is a phrase-structure grammar G = (V, T, P, S), such that every production  $p = x \rightarrow y \in P$  satisfies  $|x| \leq |y|$ .

**Definition 6.** A context-sensitive language (CS language) is language generated by a CS grammar. The family of context-sensitive languages is denoted by  $\mathcal{L}(CS)$ .

**Definition 7.** A context-free grammar (CF grammar) is a phrase-structure grammar G = (V, T, P, S), such that every production  $p = x \rightarrow y \in P$  satisfies  $A \rightarrow x$ , where  $A \in V - T$  and  $x \in V^*$ .

**Definition 8.** A context-free language (CF language) is a language generated by a context-free grammar. The family of context-free languages is denoted by  $\mathcal{L}(CF)$ .

**Definition 9.** A scattered context grammar (SCG, see [27]) is a quadruple G = (V, T, P, S), where

- V is a total alphabet;

- $T \subset V$  is a finite set of terminals;

- $S \in V T$  is the start symbol;

- P is a finite set of productions of the form  $(A_1, \ldots, A_n) \to (x_1, \ldots, x_n)$ , where  $A_i \in V T$ ,  $x_i \in V^*$  for all  $i : 1 \le i \le n$ .

**Definition 10.** A propagating scattered context grammar (PSCG) is a SCG G = (V, T, P, S), in which every  $(A_1, \ldots, A_n) \to (x_1, \ldots, x_n) \in P$  satisfies  $x_i \in V^+$  for all  $i : 1 \le i \le n$ .

**Definition 11.** Let G = (V, T, P, S) be a (propagating) SCG. If

$$y = u_1 A_1 u_2 \dots u_n A_n u_{n+1},$$

$$z = u_1 x_1 u_2 \dots u_n x_n u_{n+1},$$

and  $y, z \in V^*$ ,  $p = (A_1, \ldots, A_n) \to (x_1, \ldots, x_n) \in P$ , then y directly derives z in the SCG G according to the production  $p, y \Rightarrow_G z[p]$  (or simply  $y \Rightarrow_G z$ ).

**Definition 12.** The *(propagating) scattered context language* is a language generated by a (propagating) SCG. The family of (propagating) scattered context languages is denoted by  $\mathcal{L}((P)SC)$ .

We can see that an application of a scattered context production simulates application of several context free productions in parallel. Furthermore, scattered context grammars have another advantage over other grammar types (e.g. CS grammars) — they preserve CF grammar ability to be effectively analysed and parsed [44]. **Theorem 1.** Generative power of the previously defined language families can described as (see [55]):

$$\mathcal{L}(\mathrm{CF}) \subset \mathcal{L}(\mathrm{PSC}) \subseteq \mathcal{L}(\mathrm{CS}) \subset \mathcal{L}(\mathrm{RE}) = \mathcal{L}(\mathrm{SC}).$$

The relation  $\mathcal{L}(PSC) \subseteq \mathcal{L}(CS)$  is still an open problem.

**Definition 13.** An extended lazy finite automaton is a 7-tuple  $M = (Q, \Sigma, R, s, S, F, z)$ , where (see [35, 69])

- Q is a finite set of states;

- $\Sigma$  is an input alphabet;

- R is a finite set of transitions in the form  $pa \to q$ , where  $p, q \in Q$  and  $a \in \Sigma^*$ ;

- $s \in Q$  is the start state;

- S is a set of semantic actions;

- $F \subseteq Q$  is a set of final states;

- z is a relation  $z \subseteq R \times S$ .

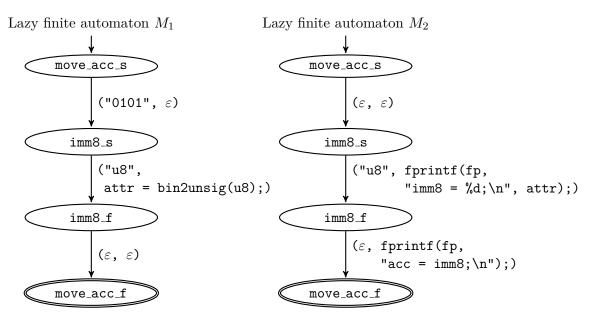

The relation z assigns the semantic actions to the particular transitions. The semantic action is an indivisible sequence of a C code, which is executed when a particular transition is taken. The further details about this formalism and its usage are described in Chapter 5. Furthermore, definitions of configuration, move, and accepted language are analogical to definitions related to a standard *lazy finite automaton*, see [35].

**Definition 14.** A two-way coupled finite automaton (see [35]) is a triple  $C = (M_1, M_2, h)$ , where

- $M_i = (Q_i, \Sigma_i, R_i, s_i, S_i, F_i, z_i)$  is an extended lazy finite automaton, i = 1, 2;

- h is a bijective mapping from  $R_1$  to  $R_2$ .

Let  $h^*$  be a mapping from  $R_1^*$  to  $R_2^*$  and

- $-h^*(\epsilon) = \{\epsilon\};$

- for every  $r_1, r_2, ..., r_n \in R_1$  applies that  $h^*(r_1, r_2, ..., r_n) = h(r_1)(r_2) ... (r_n)$  for all  $n \ge 1$ .

In other words, the automata  $M_1$  and  $M_2$  cooperate via the bijective mapping h from  $R_1$  to  $R_2$  and vice versa. The further details about this formalism and its usage are described in Chapter 5.

#### 2.2 Theory of Compiler Construction

Within this section, we define the basic terminology used within the compiler construction theory. Most of these terms are based on the graph theory; therefore, the basics of this area are reviewed at first. This section is based on [1, 6, 68].

**Definition 15.** A directed graph (or digraph) is a pair, G = (N, E), where

- N is a non-empty finite set of elements called *nodes* (vertices);

- $E \subseteq N \times N$  is a finite set of ordered pairs of nodes called *edges (arcs)*.

If  $(u, v) \in E$  then u is adjacent to v and v is adjacent from u. A predecessor of a node v is a node adjacent to v, and a successor of v is a node adjacent from v. The *indegree* of a node v is the number of predecessors of v, and the *outdegree* of v is the number of successors of v.

A walk W in G is a sequence of nodes  $v_0v_1 \dots v_n$  such that  $v_i \in N$  and  $(v_{i-1}, v_i) \in E$ for  $1 \leq i \leq n$ . The length of a walk W is the number of edges in W and it is as denoted |W|. A walk with  $v_0 = v_n$  is called *cycle*.

**Definition 16.** Basic block (BB) [15] is a sequence of statements<sup>4</sup> that are always executed together and it has a single entry point (*start address*), single exit point (*end address*), and no branch statement within it. In other words, only the last statement of a particular basic block may branch<sup>5</sup> to other basic block and only the first statement of a basic block can be a destination of any branch statement.

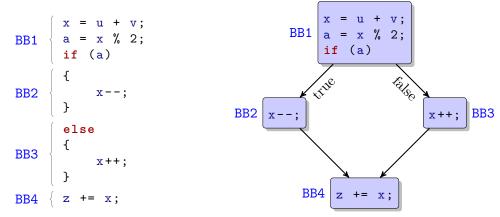

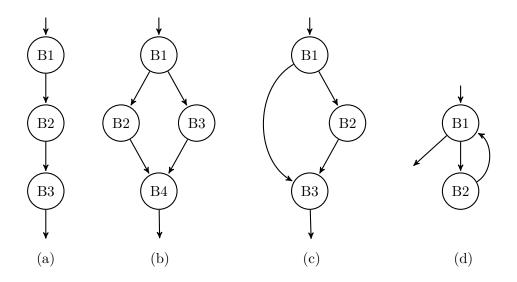

Example of source-code partitioning into basic blocks is depicted in Figure 2.1a.

(a) C source code divided into basic blocks.

(b) Control-flow graph of the source code.

Figure 2.1: Illustration of basic blocks and control-flow graph for a simple source code.

**Definition 17.** Control-flow graph (CFG) for a program P is a directed graph G = (N, E) that satisfies the following conditions:

- 1. Each node  $n \in N$  represents a basic block of P;

- 2. Each edge  $(u, v) \in E$  represents a branch from one basic block (u) to another (v);

- 3. N contains two distinguished nodes: the *initial node*  $v_I$ , which has indegree zero, and the *exit node*  $v_E$ , which has outdegree zero and through which the control flow leaves (e.g. return from application to operating system).

$<sup>^{4}</sup>$ The term *statement* is used in the meaning of HLL statement (e.g. assignment, loop, conditional statement). Moreover, all the following definitions in this sections hold for machine-code instructions too.

<sup>&</sup>lt;sup>5</sup>In the following text, the term *branch* stands for every statement that can change the flow of execution (e.g. (un)conditional branch, function call, return from function, interruption).

Nodes not occurring in any walk from  $v_I$  to  $v_E$  are called *unreachable*. An example of a control-flow graph is illustrated in Figure 2.1b.

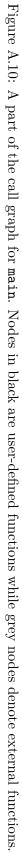

**Definition 18.** Call graph (CG) for a program P is a directed graph G = (N, E) that satisfies the following conditions:

- 1. Each node  $n \in N$  represents a function<sup>6</sup> of P;

- 2. Each edge  $(u, v) \in E$  represents a function call from function u (*caller*) to function v (*callee*);

- 3. The *initial node*  $v_I \in N$  (indegree zero) represents an entry function of the program P, denoted as main function in the following text<sup>7</sup>.

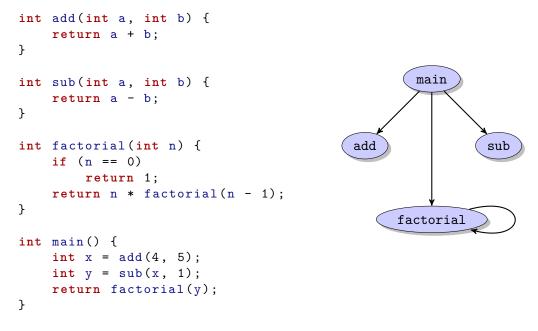

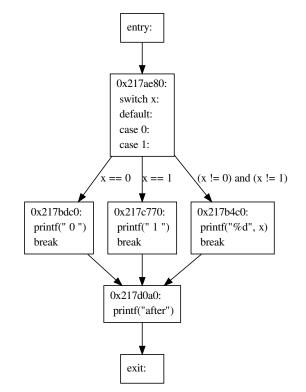

Often, a call graph is *fully connected*, i.e. the entry point of the program reaches all procedures. An example of a call graph is illustrated in Figure 2.2.

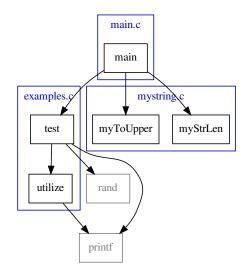

(a) C source code consisting of four functions. (b) Call graph for a given source code.

Figure 2.2: Example of a call graph.

**Definition 19.** The *definition-use graph* (def-use chain, or DU chain) [40] for a program P is a directed graph G = (N, E) that satisfies the following conditions:

1. Each node  $n \in N$  represents one statement of P; each statement may *define* or *use* one or more *variables*;

$<sup>^{6}</sup>$ With a few exceptions, the term *function* represents also other similar HLL constructions (such as *procedures*) in the following text.

<sup>&</sup>lt;sup>7</sup>This definition stands for executable files with one entry point. However, this is not true for libraries, because they have multiple entry points, and the call graph may not be fully connected.

2. Each edge  $(u, v) \in E$  represents a relation between a variable's definition in u and its usage in v during processing of P. The use of the variable (in v) must be reachable from its definition (in u) without any intervening re-definitions.

Definition-use chains are used mainly in compilers to get from a definition of a variable to all locations that could use that defined value.

**Definition 20.** The use-definition graph (use-def chain, or UD chain) is a counterpart of the definition-use graph. Each of its edges  $(u, v) \in E$  represents a relation between a statement u with variable's usage and statement v that may have defined the variable last prior to u.

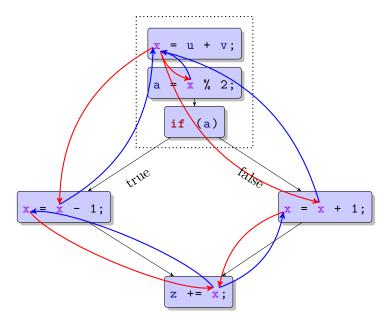

An example of def-use and use-def chains for a variable x listed in Figure 2.1 is depicted in Figure 2.3.

Figure 2.3: Example of def-use chains (red) and use-def chains (blue) for variable x.

**Definition 21.** Static Single-Assignment Form (SSA) is a form of code representation, which guarantees that each variable is assigned exactly once. This is the major difference to classical three-address code representation [1]. A short comparison of these two forms is depicted in Figure 2.4. As we can see, the original variable **a** has to be redefined as a new variable (e.g. **a1**, **a2**) each time we reassign the original variable.

| a = u + v;              | a = u + v;                         |

|-------------------------|------------------------------------|

| b = a - w;              | b = a - w;                         |

| a = b * x;              | a1 = b * x;                        |

| a = a * y;              | a2 = a1 * y;                       |

| (a) Three-address code. | (b) Static single-assignment form. |

Figure 2.4: Example of different types of intermediate-code representation.

Storage of intermediate code representation (IR) in the SSA form is common for compilers (e.g.  $LLVM^8$ ,  $GCC^9$ ) and decompilers (e.g. Boomerang). In the SSA form, use-def chains are explicit and each contains a single element. The major advantage of SSA is its positive impact on optimizations and transformations, such as expression propagation, data flow analysis (DFA), etc. For more details about SSA and its usage in decompilation, see [21].

As will be described in Chapter 6, basic blocks, control-flow graphs, and call graphs are fundamental parts of a *control-flow analysis* (CFA) used within the proposed retargetable decompiler. Furthermore, a *data-flow analysis* of this decompiler is based on use-def chains, def-use chains, and SSA form.

<sup>&</sup>lt;sup>8</sup>http://llvm.org/ <sup>9</sup>http://gcc.gnu.org/

# Chapter 3

# Focus of the Thesis

"The x86 really isn't all that complex – it just doesn't make a lot of sense."

Mike Johnson (AMD)