### **BRNO UNIVERSITY OF TECHNOLOGY** VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

FACULTY OF INFORMATION TECHNOLOGY FAKULTA INFORMAČNÍCH TECHNOLOGIÍ

DEPARTMENT OF COMPUTER SYSTEMS ÚSTAV POČÍTAČOVÝCH SYSTÉMŮ

# ADDRESSING ISSUES IN RESEARCH ON PACKET CLASSIFICATION IN CORE NETWORKS

ŘEŠENÍ PROBLÉMŮ VE VÝZKUMU KLASIFIKACE PAKETŮ V PÁTEŘNÍCH SÍTÍCH

PHD THESIS DISERTAČNÍ PRÁCE

AUTHOR AUTOR PRÁCE

SUPERVISOR ŠKOLITEL Ing. JIŘÍ MATOUŠEK

Ing. JAN KOŘENEK, Ph.D.

**BRNO 2018**

#### Abstract

Although the Internet has changed significantly since the beginning of the 21st century, packet classification is still one of the most common operations implemented in networking devices. Nevertheless, the requirements on its performance are continuously increasing, especially in core networks. Currently, packet classification algorithms have to support 100 Gbps throughput. In addition, classification rule sets are becoming larger and the number of bits involved in the classification decision is growing due to 128-bit IPv6 addresses and classification according to more than 5 header fields in the OpenFlow protocol. Therefore, the majority of contemporary research on packet classification in core networks address the performace of packet classification algorithms, which has to keep pace with continuously increasing requirements. However, the researchers also focus on benchmarking newly developed algorithms because they have to be benchmarked using real rule sets, but such data are not available for most of the packet classification use cases. This thesis deals with both of these issues because it is important not only to design packet classification algorithms having high performance but also to assess their parameters by benchmarking based on proper data sets.

Regarding the performance of packet classification algorithms, this thesis focuses on improving prefix matching, which is used in the majority of 1-dimensional and also multidimensional algorithms. Since a software implementation of prefix matching cannot fulfill the requirements imposed on packet classification in core networks, the thesis proposes a novel pipelined prefix matching architecture that targets Xilinx FPGA chips and utilizes their distributed on-chip memory. To fit the whole prefix matching data structure into FPGA's on-chip memory, this thesis also proposes a memory-efficient trie-based representation of a prefix set. The proposed representation is more memory efficient than well-known multibit tries Tree Bitmap and Shape Shifting Trie and for IPv4 prefix sets it also significantly overcomes the Prefix Partitioning lookup algorithm. The architecture then comprises two independent processing pipelines (to utilize both ports of on-chip memory blocks) that are together able to perform almost 255 million lookups per second, which translates into throughput of 170 Gbps for the shortest Ethernet frames.

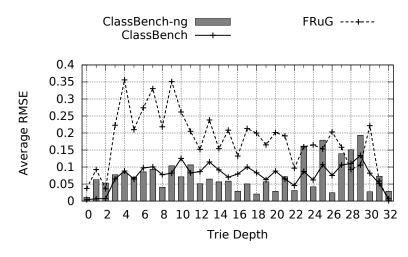

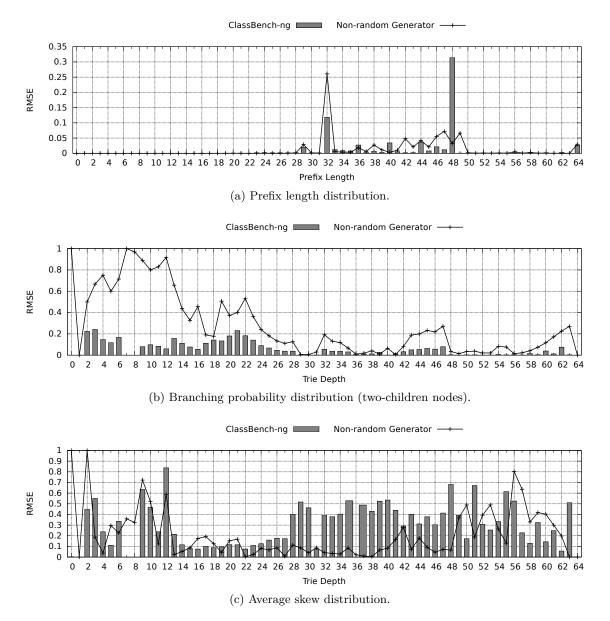

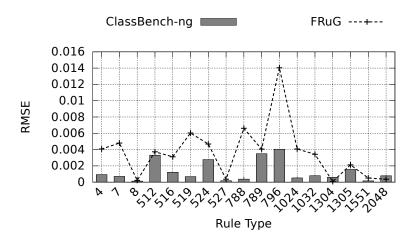

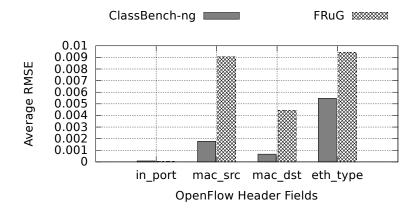

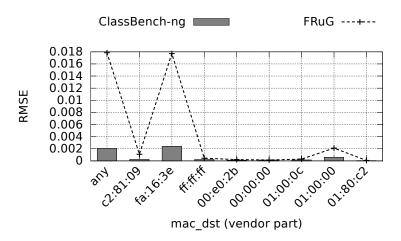

To allow realistic packet classification algorithms benchmarking, the thesis introduces a new open source synthetic rule set generator called ClassBench-ng, which integrates the generation of IPv4, IPv6, and OpenFlow 1.0.0 classification rule sets following the statistical properties specified in an input seed. Apart from the rule set generation, ClassBench-ng also supports an analysis of a real rule set in the **ovs-ofct1** format producing a corresponding seed that may be used for the generation of a similar synthetic rule set later on. Therefore, researchers having access to real classification rule sets can share their benchmarking data with other members of the community via statistical-based (thus anonymous) seeds produced by ClassBench-ng. With respect to the precision of the rule set generation process, ClassBench-ng is better than original ClassBench and FRuG in case of IPv4 prefixes and than Non-random Generator in case of IPv6 prefixes, when considering an average score for all IP prefix-related parameters. Moreover, it also clearly outperforms FRuG in the precision of OpenFlow rule sets generation.

### Abstrakt

Ačkoliv se Internet od počátku 21. století znatelně proměnil, klasifikace paketů je stále jednou z nejběžnějších operací implementovaných v síťových zařízeních. Požadavky na její výkonnost však neustále narůstají, zvláště pak v oblasti páteřních sítí, kde musejí současné klasifikační algoritmy podporovat propustnost 100 Gb/s. Navíc dochází i k nárůstu počtu používaných klasifikačních pravidel a v souvislosti se zavedením 128bitových adres v protokolu IPv6 a klasifikace paketů založené na více než 5 položkách v protokolu OpenFlow se také zvyšuje počet bitů majících vliv na výsledek procesu klasifikace. Většina současného výzkumu v oblasti klasifikace paketů v páteřních sítích se proto zaměřuje na zvyšování výkonnosti klasifikačních algoritmů, které musejí držet krok s neustále narůstajícími požadavky. Výzkumníci se však také věnují měření výkonnostních parametrů nově vyvinutých klasifikačních algoritmů, respektive generování vhodných syntetických sad klasifikačních pravidel pro tato měření, protože reálné sady pravidel nejsou pro většinu oblastí, v nichž se klasifikace paketů používá, dostupné. Tato práce se zaměřuje na obě uvedené oblasti, protože je nutné nejen vyvíjet klasifikační algoritmy s vysokou výkonností, ale také ověřovat jejich výkonnostní parametry s využitím vhodných datových sad.

V oblasti výkonnosti klasifikačních algoritmů se tato práce věnuje především úloze vyhledávání shodných prefixů, která je součástí většiny jednodimenzionálních i vícedimenzionálních klasifikačních algoritmů. Jelikož softwarová implementace vyhledávání shodných prefixů nemůže dostát požadavkům na klasifikaci paketů v páteřních sítích, tato práce navrhuje implementaci dané úlohy pomocí zřetězené architektury určené pro FPGA čipy firmy Xilinx a využívající distribuovaných paměťových bloků dostupných na těchto čipech. Kromě toho je v této práci navržena i paměťově efektivní reprezentace sady prefixů založená na binárním prefixovém stromu (tzv. trie), která umožňuje uložit celou datovou strukturu potřebnou pro vyhledávání shodných prefixů do paměti na FPGA čipu. Navržená reprezentace prefixové sady je s ohledem na paměťové nároky efektivnější než reprezentace používané ve známých vícebitových trie Tree Bitmap a Shape Shifting Trie a v případě IPv4 prefixů také výrazně překonává reprezentaci používanou algoritmem Prefix Partitioning. Samotná architektura pro vyhledávání shodných prefixů pak sestává ze dvou zřetězených linek využívajících oba dva porty paměťových bloků dostupných na FPGA čipu, které jsou dohromady schopné provést téměř 255 milionů vyhledání za sekundu, což pro nejkratší rámce protokolu Ethernet znamená propustnost 170 Gb/s.

Pro podporu realistického měření výkonnostních parametrů klasifikačních algoritmů představuje tato práce nový volně dostupný generátor syntetických sad klasifikačních pravidel nazývaný ClassBench-ng, který umožňuje generování IPv4, IPv6 a OpenFlow 1.0.0 pravidel, jejichž statistické vlastnosti odpovídají rozložením popsaným ve vstupním souboru parametrů. Kromě generování syntetických klasifikačních pravidel podporuje tento nástroj také analýzu reálných pravidlových sad ve formátu ovs-ofctl, jejímž výstupem je odpovídající soubor parametrů, který může být později použit pro generování podobné syntetické sady pravidel. Výzkumníci mající přístup k reálným sadám klasifikačních pravidel tudíž mohou sdílet svá testovací data s ostatními členy výzkumné komunity prostřednictvím souborů parametrů vytvořených nástrojem ClassBench-ng, které popisují pouze statistické vlastnosti původních pravidlových sad, a tudíž zachovávají jejich anonymitu. S ohledem na přesnost generování syntetických sad klasifikačních pravidel dosahuje nástroj ClassBench-ng lepších průměrných výsledků než nástroje ClassBench a FRuG v případě IPv4 prefixů a než nástroj Non-random Generator v případě IPv6 prefixů. Generování syntetických sad OpenFlow pravidel je pak v tomto nástroji přesnější než v nástroji FRuG.

## Keywords

Packet classification, core networks, prefix matching, FPGA, OpenFlow, ClassBench-ng.

### Klíčová slova

Klasifikace paketů, páteřní sítě, vyhledávání shodných prefixů, FPGA, OpenFlow, ClassBenchng.

## Reference

MATOUŠEK, Jiří. Addressing Issues in Research on Packet Classification in Core Networks. Brno, 2018. PhD thesis. Brno University of Technology, Faculty of Information Technology. Supervisor Ing. Jan Kořenek, Ph.D.

## Addressing Issues in Research on Packet Classification in Core Networks

#### Declaration

I hereby declare that this Ph.D. thesis is my original work written under the supervision of Ing. Jan Kořenek, Ph.D. All relevant information sources, which were used during the preparation of this thesis, are properly cited and included in the list of references.

Jiří Matoušek November 30, 2018

### Acknowledgements

First of all, I thank to my supervisor Ing. Jan Kořenek, Ph.D., for his numerous valuable comments and suggestions as well as great patience and support during the whole period of my Ph.D. studies. My thanks also go to my former supervisor doc. Ing. Zdeněk Kotásek, CSc., who took me under his wing in the first two years of this period. Further, I am grateful to Dr. Andrew W. Moore for hosting me at the Computer Laboratory, University of Cambrige, between October and December 2014 and to Dr. Gianni Antichi, who was my mentor during that visit and has virtually been my co-supervisor since that time. I thank to my co-authors for inspiring discussions and enjoyable cooperation; colleagues from the Department of Computer Systems, Faculty of Information Technology, Brno University of Technology, for their helpful comments on various parts of this thesis; and colleagues from the Security and Administration Tools department at CESNET for creating a friendly working environment. Last but not least, I am grateful to my family, friends, and my girlfriend Karolína for their endless support and patience.

The work presented in this thesis was supported by the Ministry of Education, Youth and Sports of the Czech Republic (under the CESNET E-infrastructure project LM2015042 and the IT4Innovations excellence in science project LQ1602), the Technology Agency of the Czech Republic (under the project TA03010561), the IT4Innovations Centre of Excellence project CZ.1.05/1.1.00/02.0070, and the internal BUT FIT projects FIT-S-11-1, FIT-S-14-2297, and FIT-S-17-3994. The visit to the Computer Laboratory, University of Cambridge, was supported by the Ministry of Education, Youth and Sports of the Czech Republic from the Programme of Student Mobility Support.

## Contents

| 1        | Intr | oduction                                           | 3        |

|----------|------|----------------------------------------------------|----------|

|          | 1.1  | Thesis Goals                                       | 4        |

|          | 1.2  | Thesis Organization                                | 5        |

| <b>2</b> | Pac  | ket Classification in Core Networks                | 6        |

|          | 2.1  | Definition                                         | 6        |

|          | 2.2  | Use Cases                                          | 7        |

|          | 2.3  | Approaches to Packet Classification                | 9        |

|          |      | 2.3.1 Naive Approaches                             | 0        |

|          |      | 2.3.2 TCAM 1                                       | 1        |

|          |      | 2.3.3 Representation Using Tuples 1                | 2        |

|          |      | 2.3.4 Geometric Representation                     | 4        |

|          |      | 2.3.5 Combinatorial Representation                 | 5        |

|          |      | 2.3.6 Range Matching 1                             | 6        |

|          |      | 2.3.7 Prefix Matching 1                            | 7        |

|          | 2.4  | Research Issues                                    | 7        |

|          |      | 2.4.1 Performance of Algorithms                    | 7        |

|          |      | 2.4.2 Algorithms Benchmarking                      | 9        |

| 3        | Rel  | ated Work 2                                        | 1        |

|          | 3.1  | 1-Dimensional Packet Classification Algorithms     | 21       |

|          |      | 3.1.1 Trie                                         | 22       |

|          |      | 3.1.2 Tree Bitmap                                  | 23       |

|          |      | 3.1.3 Shape Shifting Trie                          | 24       |

|          |      | 3.1.4 Multiple SRAM-based Lookup Algorithm         | 25       |

|          |      | 3.1.5 Prefix Partitioning Lookup Algorithm         | 26       |

|          | 3.2  | Multi-Dimensional Packet Classification Algorithms | 27       |

|          |      | 3.2.1 Exhaustive Search                            | 27       |

|          |      | 3.2.2 Decision Tree                                | 28       |

|          |      | 3.2.3 Decomposition                                | 31       |

|          |      | 3.2.4 Tuple Space                                  | 87       |

|          | 3.3  | 1-Dimensional Rule Set Generators                  | 9        |

|          |      | 3.3.1 Non-random Generator                         | <b>9</b> |

|          |      |                                                    | 0        |

|          | 3.4  | Multi-Dimensional Rule Set Generators              | 1        |

|          |      |                                                    | 2        |

|          |      |                                                    | 4        |

|          |      |                                                    | 4        |

| 4        | Add   | dressin | g Performance of Algorithms          | <b>47</b> |

|----------|-------|---------|--------------------------------------|-----------|

|          | 4.1   | Analy   | sis of Real Prefix Sets              | 48        |

|          | 4.2   | Propo   | sed Prefix Set Representation        | 51        |

|          | 4.3   | Propo   | sed Hardware Architecture            | 54        |

|          | 4.4   | Exper   | imental Evaluation                   | 57        |

|          | 4.5   | Summ    | hary                                 | 60        |

| <b>5</b> | Ado   | dressin | g Algorithms Benchmarking            | 62        |

|          | 5.1   | Challe  | enges in Rule Set Generation         | 63        |

|          | 5.2   | Analy   | sis of Real Rule Sets                | 64        |

|          |       | 5.2.1   | IP Prefixes                          | 64        |

|          |       | 5.2.2   | Ports and Protocol                   | 68        |

|          |       | 5.2.3   | OpenFlow                             | 70        |

|          | 5.3   | ClassI  | Bench-ng: Next Generation ClassBench | 73        |

|          |       | 5.3.1   | Improved ClassBench                  | 75        |

|          |       | 5.3.2   | IPv6 Generation                      | 78        |

|          |       | 5.3.3   | OpenFlow Analysis                    | 78        |

|          |       | 5.3.4   | OpenFlow Generation                  | 80        |

|          | 5.4   | Exper   | imental Evaluation                   | 81        |

|          |       | 5.4.1   | IPv4 Prefixes Generation             | 81        |

|          |       | 5.4.2   | IPv6 Prefixes Generation             | 83        |

|          |       | 5.4.3   | OpenFlow Rules Generation            | 83        |

|          | 5.5   | Summ    | nary                                 | 86        |

| 6        | Cor   | nclusio | ns                                   | 88        |

|          | 6.1   | Summ    | nary of Contributions                | 90        |

| Bi       | bliog | graphy  |                                      | 91        |

## Chapter 1

## Introduction

Computer networks are an indispensable part of our everyday life. We use them as a source of information and a means for communication at work as well as in our free time. The most prominent computer network today is a global network called the Internet. It evolved from research networks during 1970s and 1980s and established as a publicly available global network in 1990s. However, since the beginning of 21st century we have experienced rapid technology development that has significantly changed the Internet. The current Internet is no more the one we knew at the beginning of this century.

There are two main technological drivers of Internet changes: (1) growing transfer rates and (2) increasing number of mobile subscriptions. Significant growth of transfer rates can be illustrated on Ethernet, which is the most utilized LAN (*Local Area Network*) technology for fixed subscriptions. While the highest standardized transfer rate for Ethernet was 1 Gbps in 2000 [6], the current operational maximum is 100 Gbps [9]. In addition, since the standard for 400 Gbps Ethernet [13] has been approved in December 2017, the upgrade of the maximum transfer rate in core networks can be expected in the near future. On the other hand, accessing the Internet from mobile devices has been enabled mainly by the 802.11 family of standards [12] and the IMT-2000 standard [34], which together started the advent of mobile-broadband subscriptions. According to ITU (*International Telecommunication Union*) data [33], in 2016 there were 52.2 active mobile-broadband subscriptions per 100 inhabitants worldwide.

Technology development made access to the Internet more affordable, even in developing countries. The number of individuals using the Internet grew from 495 million in 2001 to 3385 million in 2016 [33]. Moreover, users often own several devices that are able to access the Internet (e.g., personal computer, tablet, smartphone, smart TV, or intelligent sensor). This resulted in 17.1 billion of connected devices (i.e., 2.3 devices per capita) in 2016 and forecasted growth to 27.1 billion (3.5 per capita) in 2021, as reported by Cisco [14]. Because the maximum number of distinct IPv4 (Internet Protocol version 4) addresses is less than 4.3 billion, all RIRs (Regional Internet Registries) except AFRINIC (AFRIcan Network Information Center) exhausted their IPv4 allotments between 2011 and 2015 [14]. Therefore, since 2011 we have experienced accelerated adoption of IPv6 [30], the successor of IPv4. However, not only the principal protocol of the Internet is changing. Architecture of computer networks is being redefined as well, especially due to the concept of network virtualization. Although there are numerous, often competing, technologies enabling this concept at various levels of network architecture [35], one of the most promising approaches is SDN (Software-Defined Networking), which regained interest after the introduction of OpenFlow [44], currently the most common protocol for communication between control

and data planes of a switch. Since that time, OpenFlow-based SDN has proven to be a viable approach through a number of successful deployments in networks ranging from LANs to WANs (*Wide Area Networks*) [37].

Despite all the changes of the Internet were brought to life by upgrading its infrastructure, packet classification at physical link speed is still one of the most common operations implemented in networking devices. Upon arrival, a networking device classifies every packet according to one or more of its header fields and uses the result of classification for further processing of the packet. Depending on the function of a device, the result of classification may be used for basic forwarding operation, to apply security policies, application-specific processing, or QoS (*Quality of Service*) guarantees.

Even though packet classification has not been replaced by another functionality, requirements on its performance are continuously increased. For instance, because of growth of transfer rates to 100 Gbps and extremely high utilization of the IPv4 address space, a core router has to be able to make a forwarding decision according to a forwarding table containing more than 680 thousand IPv4 prefixes [3] every 6.72 ns. With respect to the IPv6 protocol, due to 4-times longer IP address involved in the forwarding process, the situation is even worse. Currently, the number of IPv6 prefixes in a forwarding table of core routers is almost 43 thousand [3]; however, this number is expected to grow together with IPv6 penetration. Another example of growing demands on packet classification is extending the set of packet header fields involved in the classification process. While the most common set of header fields involved in packet classification consists of 5 header fields, the OpenFlow protocol initially extended this set to 12 fields [7] and the latest version of the OpenFlow protocol defines packet classification based on 45 fields [10]. Both these examples demonstrate that packet classification requires continuous attention of researchers.

From a high level perspective, there can be identified two issues that are addressed in the research on packet classification in core networks.

The first issue is related to the performance of packet classification algorithms, which has to keep pace with growing transfer rates. Parameters that have the greatest influence on the performance are the number of bits involved in packet classification (i.e., the number of utilized header fields and their length) together with the number of utilized classification rules. Therefore, new algorithms have to deal with growing popularity of SDN-based network virtualization utilizing the OpenFlow protocol (more fields) [35] and/or increasing IPv6 penetration (longer fields) [30]. Moreover, since current CPUs (*Central Processing Units*) do not provide enough performance for even 1-dimensional packet classification according to destination IP address (i.e., IP lookup) on a 100 Gbps link, packet classification algorithms targeting core networks have to be accelerated in hardware.

The second issue is related to benchmarking packet classification algorithms, which are continuously improved to meet ever-increasing requirements on their performance. Because real classification rule sets are not usually available for benchmarking, researchers designed and implemented several tools capable of generating synthetic rule sets [66, 67, 63, 59, 29]. Nevertheless, even together these tools are not able to generate all data sets necessary for benchmarking current packet classification algorithms. In addition, it can be shown that the process of rule set generation in the currently available tools is not always accurate.

#### 1.1 Thesis Goals

This thesis aims to address identified issues in the research on packet classification in core networks via achieving the following two goals. The **first goal** is to address the issue related to the performance of packet classification algorithms by designing a hardware-accelerated prefix matching algorithm that will be able to achieve 100 Gbps throughput for both IPv4 and IPv6 protocols.

The **second goal** is to address the issue related to benchmarking new packet classification algorithms using a tool capable of generating synthetic IPv4, IPv6, and OpenFlow 1.0.0 rule sets with parameters similar to real rule sets.

#### 1.2 Thesis Organization

A brief introduction of the research area and the goals of the thesis in Chapter 1 is followed by their detailed description in Chapter 2. Firstly, this description focuses on the definition of packet classification and its typical use cases. It also presents various 1-dimensional and multi-dimensional approaches to packet classification, which form the basis of current packet classification algorithms. The last section of Chapter 2 then contains a detailed discussion of two main issues in the research on packet classification that are addressed by the goals of this thesis.

Before addressing the performance of packet classification algorithms (the first issue) and their benchmarking (the second issue), the thesis summarizes previous work related to these issues in Chapter 3. With respect to the first issue, related work is represented by selected packet classification algorithms. On the other hand, the second part of this chapter presents several generators, which are able to produce synthetic classification rule sets that are utilized when addressing the second issue. In the whole chapter, 1-dimensional and multi-dimensional approaches are described separately.

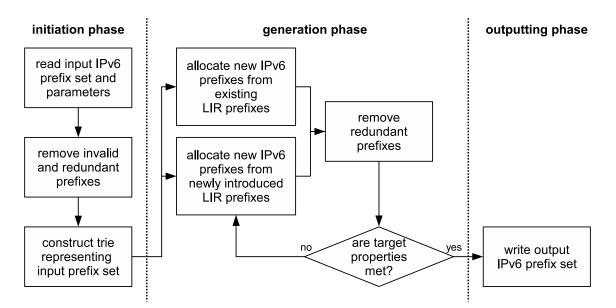

The first issue in research on packet classification is addressed in Chapter 4. The core of this chapter describes a memory-efficient IP prefix set representation and a hardware architecture implementing IP lookup using this representation. The chapter also contains an analysis of properties of real IP prefix sets and an experimental evaluation of both the IP prefix set representation and the hardware architecture, including their comparison to related work.

Chapter 5 addresses the second issue in packet classification research. The first part of the chapter is devoted to a detailed analysis of real classification rule sets. After that, ClassBench-ng, a new tool capable of generating synthetic rule sets, is introduced and its properties are compared with other similar tools.

The thesis is concluded with Chapter 6 that evaluates the proposed goals, summarizes contributions of the thesis and outlines possible future work in the given research area.

## Chapter 2

## Packet Classification in Core Networks

The main aim of this chapter is to introduce the area of packet classification and discuss in details related research issues. First of all, Section 2.1 defines the term packet classification and introduces various ways of specifying conditions that form a classification rule. To support the claim that packet classification is utilized in virtually every networking device, Section 2.2 describes typical use cases of this operation along with the most common formats of classification rules. Next, Section 2.3 is devoted to 1-dimensional as well as multi-dimensional approaches to packet classification, which represent the key ideas behind current packet classification algorithms. The chapter is concluded in Section 2.4 containing the discussion of issues addressed in the current research on packet classification, especially in core networks. Because of continuously increasing requirements on the performance of packet classification algorithms, research in this area is still ongoing and it is centered around the performance of packet classification algorithms and their benchmarking.

#### 2.1 Definition

Packet classification is a process determining a class (often referred to as a network flow) that a packet belongs to. The input of packet classification consists of selected header fields extracted from the packet and a set of classification rules with defined priorities, in which each rule represents one class. A classification rule defines a condition for every header field extracted from input packets. The condition is usually specified in one of the following four ways.

- Value exactly one allowed value (typical for transport layer protocol).

- **Prefix** a range of allowed values having a common binary prefix (typical for source and destination IP addresses).

- **Range** an arbitrary range of allowed values (typical for source and destination transport layer ports).

- Wildcard any value is allowed (typical for header fields not important for the corresponding class).

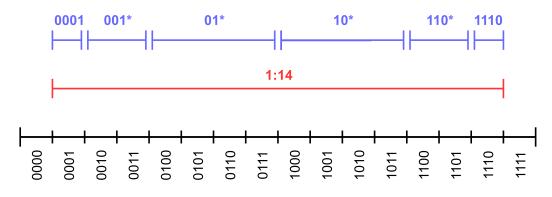

The most general of the presented specifications is the range because every other specification can be represented as a single range. However, a condition using the range specification is the most difficult to verify. Therefore, the prefix specification is often used as a uniform way of specifying a condition. An exact value and a wildcard can be replaced by a single prefix of maximum and zero length, respectively, but the number of prefixes required for replacing a range is 2l - 2 [46], l being the length of the corresponding header field, in the worst case. Such a scenario is shown in Figure 2.1.

Figure 2.1: Example of replacing the range 1:14 (red interval) on a 4-bit header field by a set of  $2 \cdot 4 - 2 = 6$  prefixes (blue intervals).

For the sake of completeness, it should be noted that any of the specifications can also be replaced by a set of exact values containing one item for each value from the specified range. On the other hand, the wildcard specification can only replace special cases of a range (full range) and a prefix (empty prefix).

Regardless the utilized specification, a condition is satisfied when the corresponding header field of a packet contains one of the allowed values. If all conditions of a classification rule are satisfied, then the packet belongs to the corresponding class. Note that classes may overlap, thus multiple classification rules can match the packet. In such a case the matching rule with the highest priority is selected as the output of packet classification. Since packet classes usually define specific processing for their packets, the output of packet classification can also be an action that is going to be applied on the classified packet.

#### 2.2 Use Cases

Packet classification is implemented in a vast majority of networking devices deployed in operating environments ranging from small edge networks to core networks forming the backbone of the Internet. Although each implementation complies with the definition presented in the previous section, its details may vary according to a specific scenario it is used in. The most common use cases of packet classification are briefly introduced in the following list. For the sake of clarity, the list does not present each use case individually, but it focuses on five categories that group similar use cases together.

**Routing.** In these use cases, the result of packet classification determines a route to a packet's destination. The simplest form of routing—IP routing—is based on matching a destination IP address only. However, routing may also be based on more sophisticated policies employing packet classification according to multiple header fields (e.g., routing packets with the same destination IP address but different transport layer protocol via different links).

- **Packet filtering.** This group of packet classification use cases belongs to the area of network security. Each classification rule defines a specific action (e.g., accept, drop, reject, intercept) applied to a corresponding network flow (i.e., to all packets that are matched by the rule). The most common example of packet filtering is a firewall, which is able to filter network traffic flowing through a given point of a network. For instance, a firewall deployed at the border of a network may filter malicious traffic destined for the network. Another use case of packet filtering is represented by lawful interception systems implementing the interception of communication specified by law enforcement agency in the course of a criminal investigation.

- Application-specific processing. Similarly to packet filtering, packet classification allows to process the traffic of a specific application—as long as it can be characterized by header fields utilized in a classification rule—differently from other traffic. Nevertheless, a set of actions that can be used for processing the traffic is richer than in the packet filtering case. Even though it is not the only example of application-specific processing, a typical use case in this group is the application of QoS guarantees via traffic shaping (i.e., delaying packets of some or all network flows in order to achieve a desired traffic profile).

- **Traffic management.** Packet classification may also be used for intelligent traffic management that allows to treat network flows differently from each other rather than in the same way. For instance, load balancing and rate limiting enriched by the notion of network flows can perform fine-grained management decisions that do not affect flows carrying sensitive network traffic. Using packet classification, service providers can also do traffic accounting and billing on a per-user basis, even when all users access the service via a shared link.

- **SDN.** Although this group does not really introduce any new use cases, it highlights the utilization of packet classification in a data plane of SDN-enabled devices. With the help of a programmable control plane an SDN architecture can therefore implement any of the already introduced uses cases. Clearly, an SDN Controller can either install necessary rules into flow tables of an SDN Datapath (e.g., for IP routing, policy-based routing, and firewall) or instruct the SDN Datapath to send packets not matching any rule to the SDN Controller for further processing (e.g., for lawful interception, accounting, and billing).

In different use cases, the number of header fields involved in the packet classification process ranges from a single field (destination IPv4/IPv6 address in case of IP routing) up to 45 fields (classification based on OpenFlow 1.5.1 [10]). Table 2.1 specifies the structure of the most often utilized types of packet classification rules that are also considered further in the thesis. Mapping of labels used in the table to particular header fields is as follows.

- *in\_port* input port number

- *mac\_src* source MAC address

- $mac\_dst$  destination MAC address

- *eth\_type* EtherType

- *vlan\_id* VLAN ID

- *vlan\_prio* VLAN priority

- *ip\_tos* DSCP (originally ToS)

- *ip\_proto* IP protocol

- *ip\_src* source IP address (IPv4 or IPv6)

- *ip\_dst* destination IP address (IPv4 or IPv6)

- *l4\_src* source TCP/UDP port

- $l_{4}dst$  destination TCP/UDP port

| Header Field   | $in\_port$ | $mac\_src$ | $mac\_dst$ | $eth\_type$ | $vlan\_id$ | $vlan\_prio$ | $ip\_tos$ | $ip\_proto$ | $ip\_src~(\mathrm{IPv4})$ | $ip\_src~(\mathrm{IPv6})$ | $ip\_dst \; (\mathrm{IPv4})$ | $ip\_dst \; (\mathrm{IPv6})$ | $l4\_src$ | $l_{4\_}dst$ |

|----------------|------------|------------|------------|-------------|------------|--------------|-----------|-------------|---------------------------|---------------------------|------------------------------|------------------------------|-----------|--------------|

| Data Width [b] | x          | 48         | 48         | 16          | 12         | 3            | 6         | 8           | 32                        | 128                       | 32                           | 128                          | 16        | 16           |

| IPv4 prefix    |            |            |            |             |            |              |           |             |                           |                           | 1                            |                              |           |              |

| IPv6 prefix    |            |            |            |             |            |              |           |             |                           |                           |                              | 1                            |           |              |

| IPv4 5-tuple   |            |            |            |             |            |              |           | ✓           | ✓                         |                           | ✓                            |                              | ✓         | ✓            |

| IPv6 5-tuple   |            |            |            |             |            |              |           | ✓           |                           | ✓                         |                              | 1                            | ✓         | ✓            |

| OpenFlow 1.0.0 | 1          | 1          | 1          | 1           | 1          | 1            | 1         | 1           | 1                         |                           | 1                            |                              | 1         | 1            |

Table 2.1: Packet header fields utilized in various types of classification rules considered in this thesis. The table also shows standard data width of each field (data width of *in\_port* depends on a specific implementation).

While some types of classification rules specified in Table 2.1 differ from each other by the version of IP protocol only (i.e., IPv4 vs. IPv6), others utilize a different number of header fields and are used in different use cases. A typical use case of a single destination IPv4/IPv6 prefix is IP routing. Next, 5 header fields of an IPv4/IPv6 5-tuple are used in many use cases, for instance in a firewall to name just one of them. Last but not least, OpenFlow 1.0.0 rules allowing specification of a condition for up to 12 header fields are used for various purposes in SDN-enabled networks, for example in datacenters.

#### 2.3 Approaches to Packet Classification

The problem of packet classification has been approached in many different ways that are described in this section. To facilitate an understanding of these approaches, they are illustrated on classification of the packet P with address = 110 and port = 110 using a rule set from Table 2.2, which is used as a running example throughout this section. The rule set utilized in the running example consists of rules specifying an address prefix and a port range, both on corresponding 3-bit header fields. The priority of the rules is descending with their position in the rule set (i.e., the first rule has the highest priority).

Apart from publications cited in particular subsections, the whole section is based on information gathered from [46, 60, 8].

| Rule | Address | Port |

|------|---------|------|

| R1   | 0*      | 5:7  |

| R2   | *       | 6:6  |

| R3   | 010     | 0:7  |

| R4   | 11*     | 5:7  |

| R5   | 11*     | 1:4  |

Table 2.2: An example rule set for 2-dimensional packet classification according to 3-bit header fields *address* and *port*. The rules are sorted from the highest to the lowest priority.

#### 2.3.1 Naive Approaches

The simplest approach to packet classification is a linear search of a rule set with rules sorted from the highest to the lowest priority. An input packet is sequentially matched against classification rules and the first matching rule is selected as the output of packet classification. Such an early termination is correct because if there are other matching rules, they will have lower priority. In the running example introduced at the beginning of Section 2.3, the linear search stops after matching the packet P against the rule R2, although the rule R4 also matches the packet.

Both search time and memory requirements of this approach are linear with respect to the number of rules. While linear search time represents the worst performance among the presented approaches, linear memory requirements are close to the optimal solution (note that different rules may redundantly use the same condition for a particular header field). Because of its search performance, this approach is feasible only for small rule sets, for example the one from Table 2.2, in which a search takes 5 steps in the worst case.

An orthogonal approach trades-off memory requirements for better search time by precomputing the best matching rule for every possible packet and storing this information into a table. Classification of an incoming packet then consists of addressing the table by concatenated header field values and reading the best matching rule information. This is illustrated using Table 2.3, which shows an excerpt of a precomputed best-matching-rule table for the running example. The excerpt is centered around the entry indicating that the rule R2 is the best matching rule for the packet P with address = 110 and port = 110.

| Address | Port | Rule |

|---------|------|------|

| :       | :    | :    |

| 110     | 100  | R5   |

| 110     | 101  | R4   |

| 110     | 110  | R2   |

| 110     | 111  | R4   |

| 111     | 000  | N/A  |

| •       | ÷    | :    |

Table 2.3: An excerpt of a precomputed best-matching-rule table for the example rule set (Table 2.2). The best matching rule for the last entry is not available (N/A) because no rule matches the corresponding packet.

Search time of this second naive approach is constant (classification is done in a single step) but its memory requirements are exponentially dependent on the number of bits involved in the classification process. The example rule set from Table 2.2 classifies packets according to two 3-bit header fields, thus the corresponding table of best matching rules consists of  $2^{3+3} = 64$  items. However, in a real-world example of packet classification according to the IPv4 5-tuple, the required table size is  $2^{32+32+8+16+16} = 2^{104}$  items, even for a rule set containing only a few rules. Therefore, despite its excellent search time, this approach to packet classification is important mainly from a theoretical point of view.

#### 2.3.2 TCAM

Another straightforward approach to packet classification is to use TCAM (*Ternary Content-Addressable Memory*). This special kind of memory is based on CAM (*Content-Addressable Memory*), which consists of rows addressed by their content. The output of CAM is the address of a row, whose content matches the input value. While CAM supports only exact matching of the input value, TCAM extends matching functionality to so-called ternary matching. Apart from the bit values 0 and 1, a row can also contain the bit value X (don't care), which allows the input to contain an arbitrary value at the corresponding position.

Since TCAM supports addressing by content and ternary matching, it can be viewed as the second naive approach with the ability to use the prefix specification. Indeed, each TCAM record (i.e., a rule after the conversion of all conditions to prefixes augmented by the X value for each unspecified bit) represents all entries of the second naive approach's table that correspond to the packets matching the record. The number of TCAM records is thus usually significantly smaller than the number of entries in the best-matching-rule table of the second naive approach. Nevertheless, the use of the prefix specification causes that more than one record may match a given packet. Therefore, packet classification based on TCAM has to consist of ternary matching an input packet in TCAM and the following selection of the highest priority rule among those associated with the matching TCAM records. Table 2.4 shows TCAM records representing the running example's rule set (see Table 2.2). The example packet P is matched by records 3 and 6, which have associated rules R2 and R4, respectively. Because of its higher priority, the rule R2 is selected as the best matching one.

| #              | Address | Port | Rule          |

|----------------|---------|------|---------------|

| 1              | OXX     | 101  | $\mathbf{R1}$ |

| 2              | OXX     | 11X  | $\mathbf{R1}$ |

| 3              | XXX     | 110  | R2            |

| 4              | 010     | XXX  | R3            |

| 5              | 11X     | 101  | R4            |

| 6              | 11X     | 11X  | R4            |

| $\overline{7}$ | 11X     | 001  | R5            |

| 8              | 11X     | 01X  | R5            |

| 9              | 11X     | 100  | R5            |

Table 2.4: TCAM records created by the range-to-prefix conversion of rules from the rule set in Table 2.2. The table also shows an original rule associated to each TCAM record. Note that records with the same associated rule do not overlap (i.e., they cannot match the same packet).

Parallel matching of the input against all rows allows constant search time of TCAM, but only at a price of increased utilization of hardware resources. Unlike the second naive approach, TCAM has to explicitly store each rule using the number of bits equal to the width of concatenated header fields. On the other hand, requirements on TCAM's capacity are linear with respect to the size of a represented rule set. However, it is important to note that because of the range-to-prefix conversion, the number or utilized records may be higher than the number of represented rules. For instance, 5 rules of the example rule set utilize 9 TCAM records, as shown in Table 2.4.

Constant search time and reasonable memory requirements are arguments behind the extensive use of TCAM in commercial devices. Nevertheless, this approach suffers from several non-negligible issues. Parallel matching, which allows constant search time, leads to high power consumption of this kind of memory. Because of supporting ternary matching, its cost per bit is also higher than of other memories. Moreover, if TCAM is used for packet classification, its capacity is not utilized efficiently due to rules replication during the range-to-prefix conversion. Last but not least, the need for storing records of width equal to the number of bits involved in packet classification limits scalability of this approach to classification according to more and/or longer header fields. All these disadvantages motivate research in algorithmic solutions to packet classification.

#### 2.3.3 Representation Using Tuples

The representation of the packet classification problem using tuples has been introduced by Srinivasan, Suri, and Varghese in [56]. It is the first out of three seminal approaches to multi-dimensional packet classification described in the thesis. In this approach, each classification rule is represented by a tuple, whose elements define the number of bits used for specification of the corresponding rule's conditions. Such a representation is motivated by the observation that real rule sets contain only a few combinations of specification lengths. Therefore, the number of distinct tuples representing a rule set is expected to be much lower than the actual number of rules.

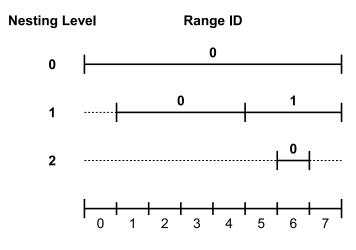

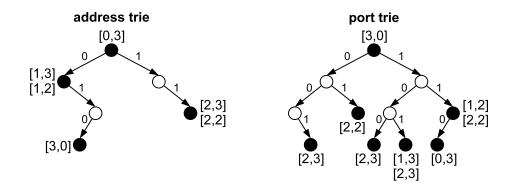

While the number of bits used in the value, wildcard, and prefix specifications is clear, the value of tuple elements corresponding to the range specification is not so straightforward to obtain. To overcome limitations of the range-to-prefix conversion, the authors of the approach proposed an alternative representation of utilized ranges that is based on a hierarchy of non-overlapping ranges. In the hierarchy, ranges are organized into several levels with the highest level containing the most general (i.e., the longest) ranges and each successive layer containing more specific (i.e., shorter) ranges than the previous level. Each range is then represented by a pair (*nesting level, range ID*), which characterizes its position within the hierarchy. The hierarchy of ranges used in the example rule set (Table 2.2) as well as *nesting level* and *range ID* of the ranges are shown in Figure 2.2.

Even though *nesting level* does not precisely characterize the number of bits used in the range specification, its meaning is similar. Clearly, *nesting level* of the full range (equal to the wildcard specification) will always be 0, while its value for the shortest ranges (equal to the value specification) will always be maximal. Therefore, the authors of [56] proposed to represent a range in a tuple by its *nesting level* and to replace the range itself by its *range ID*. Following this encoding scheme, Table 2.5 shows the example rule set (Table 2.2) together with tuples representing its rules. Note that rules R4 and R5 are represented by the same tuple, although they specify different ranges.

Figure 2.2: The hierarchy of port ranges from the example rule set (Table 2.2). The figure also shows *nesting level* and *range ID* values assigned to individual ranges.

| Rule | Address | Port | Tuple  |

|------|---------|------|--------|

| R1   | 0*      | 1    | [1, 1] |

| R2   | *       | 0    | [0, 2] |

| R3   | 010     | 0    | [3, 0] |

| R4   | 11*     | 1    | [2, 1] |

| R5   | 11*     | 0    | [2, 1] |

Table 2.5: The example rule set (Table 2.2) and tuples representing its rules. Port ranges are replaced by their range ID.

Classification of an incoming packet using a rule set represented by tuples is done by a (possibly parallel) linear search of a tuple set. Each tuple represents a subset of the original rules that is searched for a matching rule using only a limited amount of information from packet's header fields. In case of conditions specified by a value, a wildcard, or a prefix, the number of utilized bits is directly given in the tuple. However, in case of the range specification, the search utilizes *range ID* of a range that matches the corresponding header field and appears in a hierarchy of ranges at *nesting level* specified in the tuple. The search for a matching rule within the tuple is thus the exact matching problem, which can be for example solved using a hashing table. Unfortunately, the representation of a rule set using tuples does not respect rules' priorities, thus the linear search cannot be terminated prematurely (like in the first naive approach described in Section 2.3.1) and all tuples have to be searched. If the searches of multiple tuples return a matching rule, the highest priority rule is selected as the best matching one.

Classification of the packet P from the running example, introduced at the beginning of Section 2.3, using the example rule set represented by tuples is illustrated in Table 2.6. The table shows the information from packet's header fields that is utilized when particular ranges are searched for a matching rule. The utilized information match rule's conditions in case of rules R2 and R4 (c.f. Table 2.5), which belong to tuples [0, 2] and [2, 1]. Since the rule R2 has higher priority than the rule R4, it is selected as the output of packet classification.

| Tuple  | Address Bits | Range ID | Rule |

|--------|--------------|----------|------|

| [1, 1] | 1            | 1        | N/A  |

| [0, 2] | -            | 0        | R2   |

| [3, 0] | 110          | 0        | N/A  |

| [2, 1] | 11           | 1        | R4   |

Table 2.6: Address bits and *range ID* used while searching particular tuples from Table 2.5 for rules matching the running example's packet P. The table also shows found matching rules (or N/A if a tuple does not contain a matching rule).

#### 2.3.4 Geometric Representation

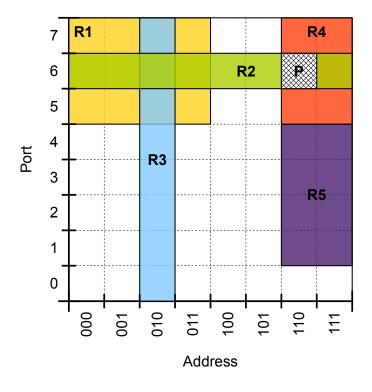

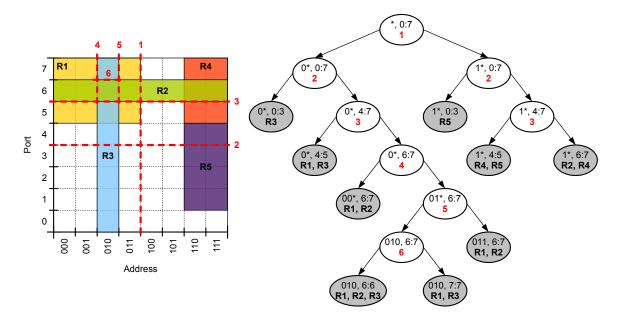

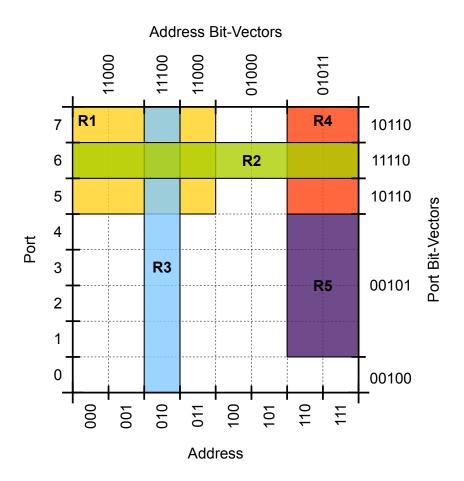

Another representation of the general packet classification problem is based on multidimensional space where each dimension corresponds to one header field utilized in packet classification. In this space, each condition of a classification rule can be represented as an interval in the corresponding dimension, thus the rule is equal to a multi-dimensional rectangle defined by intervals corresponding to its conditions. Since a packet contains exact values in its header fields, it is represented as a point in the multi-dimensional space. The geometric representation of the running example introduced at the beginning of Section 2.3 is shown in Figure 2.3. The figure shows 2-dmensional rectangles representing the example rule set (Table 2.2) as well as a point representing the example packet P.

In case of a geometrically represented rule set, a rule matching an input packet is represented by a rectangle that contains a point of the multi-dimensional space that corresponds

Figure 2.3: The geometric representation of the example rule set from Table 2.2 and the example packet P.

to the packet. As can be seen in Figure 2.3, rectangles representing rules can overlap, which illustrates a situation when more than one rule match an input packet. For instance, in Figure 2.3, both rules R2 and R4 match the packet P. Therefore, because of its higher priority, rule R2 is selected as the output of packet classification.

#### 2.3.5 Combinatorial Representation

The last seminal approach to multi-dimensional packet classification described in this thesis is based on viewing a classification rule as a combination of the given number of conditions. In order to speed up a classification process, this approach builds a Cartesian product of sets of conditions utilized in particular dimensions. The entries of the Cartesian product correspond to all possible combinations of matching results for individual dimensions and each entry has the best matching rule associated to it. This is similar to the second naive approach to packet classification. However, the condition sets of particular dimensions of a real rule set are usually significantly smaller than the number of rules in the rule set [31]. Therefore, the number of Cartesian product entries is much smaller than the number of all possible packets.

Table 2.7 shows the Cartesian product entries along with assigned best matching rules that together represent the example rule set from Table 2.2. Five out of the sixteen entries (1, 6, 11, 13, and 16) directly correspond to the original rules. Another five entries (2, 9, 10, 12, and 14) have associated the best matching rule, i.e., the highest priority rule that matches all input packets, which are matched by the conditions specified for particular dimensions in the entry. However, because the example rule set does not contain a default rule (i.e., a rule with the wildcard specification in all dimensions, which matches every packet), six entries of the Cartesian product (3, 4, 5, 7, 8, and 15) have no associated best matching rule.

| #              | Address | Port | Rule | #  | Address | Port | Rule          |

|----------------|---------|------|------|----|---------|------|---------------|

| 1              | 0*      | 5:7  | R1   | 9  | 010     | 5:7  | R1            |

| 2              | 0*      | 6:6  | R1   | 10 | 010     | 6:6  | $\mathbf{R1}$ |

| 3              | 0*      | 0:7  | N/A  | 11 | 010     | 0:7  | R3            |

| 4              | 0*      | 1:4  | N/A  | 12 | 010     | 1:4  | R3            |

| 5              | *       | 5:7  | N/A  | 13 | 11*     | 5:7  | R4            |

| 6              | *       | 6:6  | R2   | 14 | 11*     | 6:6  | R2            |

| $\overline{7}$ | *       | 0:7  | N/A  | 15 | 11*     | 0:7  | N/A           |

| 8              | *       | 1:4  | N/A  | 16 | 11*     | 1:4  | R5            |

Table 2.7: The entries of a Cartesian product created from the sets of unique conditions utilized in *address* and *port* dimensions of the example rule set (Table 2.2). If it exists, the best matching rule from the example rule set is associated with a Cartesian product's entry. Otherwise, the best matching rule is set to N/A.

Packet classification based on combinatorial representation of the rule set fully utilizes properties of the constructed Cartesian product. First of all, matching conditions for individual dimensions are determined, possibly using different 1-dimensional packet classification approaches in each dimension. As mentioned in Section 2.3.6, some approaches to 1-dimensional packet classification may return more than one matching result. Therefore, combining the matching results from individual dimensions together may lead to multiple corresponding Cartesian product's entries, each of which may have associated the best matching rule. The packet classification process is finalized by selecting the highest priority rule among these rules.

Considering the running example's packet P, prefix matching on the address field will return a single matching prefix 11<sup>\*</sup> while range matching on the port field will return a set of matching ranges ([5:7], [6:6], and [0:7]). Combinations of these matching results are represented by entries 13, 14, and 15 of the Cartesian product, the first two of which has associated the best matching rules R4 and R2, respectively (see Table 2.7). Since rule R2 has higher priority, it is the output of classification of the packet P.

#### 2.3.6 Range Matching

Apart from approaches to multi-dimensional packet classification, there are also specific approaches to 1-dimensional packet classification. They reflect different condition specifications utilized in classification rules. Since matching the value specification (exactly one value matches) and the wildcard specification (every value matches) is trivial, the next two sections will focus on matching range and prefix specifications, both of which define a set of matching values.

As already mentioned, the range specification is the most general among all the specifications, but also the most difficult for matching. Some approaches try to avoid range matching using the range-to-prefix conversion. However, the worst-case number of prefixes required for replacing a single range is 2l - 2 [46], where l is the length of the corresponding header field. Therefore, it is beneficial to have the option of direct range matching when classification rules contain the range specification.

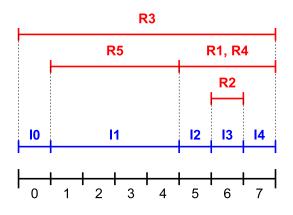

The seminal range matching approach to 1-dimensional packet classification has been introduced by Lakshman and Stiliadis in [38]. It is based on non-overlapping intervals (often referred to as elementary intervals), which are created by dividing the full range by start and end points of each range utilized in a rule set. For example, Figure 2.4 shows elementary intervals created by port ranges utilized in the example rule set (Table 2.2). In this example, rules R1 and R4 utilize the same range and several start/end points have the same value, thus the full range is divided to only 5 elementary intervals. Nevertheless, each of N classification rules may utilize a unique range and a start point as well as an end point of each range (including the full range) may be a unique value. If this worst case happens, the number of elementary intervals is 2N + 1.

Figure 2.4: Elementary intervals (blue) created by port ranges (red) utilized in the example rule set (Table 2.2). The figure also shows rules that use particular ranges.

In order to allow packet classification, each elementary interval has to store a list of classification rules, whose range overlaps with the interval. In Figure 2.4, the list is illustrated by the name of rules utilizing port ranges that are above the elementary interval. Packet classification then consists of the search for an elementary interval covering the header field value extracted from a packet, followed by returning the list of overlapping (i.e., matching) rules. For example, the packet P from the running example introduced at the beginning of Section 2.3 has the port field set to 110. Because this value is covered by interval I3, the packet's port value is matched by rules R1, R2, R3, and R4 (see Figure 2.4). The covering elementary interval can be find by an arbitrary range location algorithm, for instance binary search.

#### 2.3.7 Prefix Matching

Similarly to range matching, prefix matching is beneficial especially when classification rules contain the prefix specification. However, the prefix specification is also often used as a uniform way of specifying a condition in a classification rule. Even though the range specification is more general and more than one prefix may be necessary for replacing a single range, prefix matching is easier to implement.

The most utilized prefix matching approach to 1-dimensional packet classification is called LPM (*Longest Prefix Matching*). This approach looks for all prefixes matching the input value and returns the longest one (i.e., the most specific one) as the best matching prefix. For example, consider the running example's packet P with *address* = 110, which was introduced at the beginning of Section 2.3. Its address is matched by address prefixes utilized in rules R2 and R4/R5 (note that rules R4 and R5 use the same prefix) of the example rule set (Table 2.2). However, since the address prefix of rules R4/R5 is the longest one among them, it is the only result of LPM.

Some packet classification algorithms based on combinatorial representation might require prefix matching that returns all matching prefixes instead of just the longest one. In such a case, LPM can be easily modified to satisfy this requirement by omitting its last step.

#### 2.4 Research Issues

Current research on packet classification techniques for core networks faces two issues. The first one can be characterized as *performance of packet classification algorithms*. Clearly, the performance of classification algorithms has to be increased to meet ever-increasing requirements on packet classification in core networks. The second issue rises from the first one and it revolves around *packet classification algorithms benchmarking*. As new classification algorithms are designed, it is necessary to benchmark their performance and compare their properties to each other.

While addressing performance of packet classification algorithms and their benchmarking represent the core of this thesis (see Chapters 4 and 5, respectively), the following sections introduce the addressed issues.

#### 2.4.1 Performance of Algorithms

Even though the Internet is still growing and accelerating, packet classification stays one of the most common operations implemented in networking devices. Nevertheless, the changes of the Internet increase requirements on the performance of packet classification algorithms, which has to keep pace with growing transfer rates. The standard for 400 Gigabit Ethernet [13] has been approved in December 2017, but current core networks widely support 100 Gigabit Ethernet defined in [9]. Therefore, packet classification algorithms targeted at core networks are required to support throughput of 100 Gbps.

Considering a 64-byte Ethernet frame (i.e., the shortest frame) together with 7-byte Preamble, 1-byte SFD (*Start Frame Delimiter*), and 12-byte interpacket gap (i.e., the shortest gap), the maximum packet rate of 100 Gigabit Ethernet is approximately 148.81 MPPS (*Million Packets Per Second*). Thus, packet classification algorithms have to be able to provide a classification result every 6.72 ns. To achieve such matching performance, their designers have to deal with growing requirements on selected parameters, which include the number of bits involved in packet classification (i.e., the number of utilized header fields and their length) and the number of specified classification rules.

The number of bits involved in packet classification depends on a specific use case. However, in general it is increasing because nowadays more as well as longer header fields are being utilized in packet classification. Extensions of the set of utilized header fields are closely related to growing interest towards network virtualization, which may be realized, for instance, by OpenFlow-based SDN [35]. Each version of the OpenFlow protocol incrementally extended the set and its latest version has defined packet classification according to 45 header fields [10]. On the other hand, longer header fields are mainly due to increasing IPv6 penetration [30]. Compared to IPv4, the length of both source and destination addresses has been quadrupled in IPv6.

While the exact number of utilized header fields may vary according to the used version of the OpenFlow protocol (e.g., OpenFlow 1.0.0 utilizes "only" 12 header fields), IPv6 always requires supporting 128-bit address prefixes. Therefore, with respect to the number of bits involved in packet classification, supporting IPv6 may be more expensive than supporting additional header fields. This can be illustrated using types of classification rules from Table 2.1. Comparing packet classification based on an IPv6 prefix and an IPv4 5-tuple, the former involves 128 bits while the latter involves 104 bits. Moreover, the situation is the same when comparing an IPv6 5-tuple and OpenFlow 1.0.0 (296 bits vs. x + 237 bits).

The number of specified classification rules varies even for different instances of the same use case. In case of IP routing, forwarding tables of core routers currently contain 680 thousand IPv4 and 43 thousand IPv6 prefixes [3] but these numbers continuously grow as the allocation of prefixes from IPv4 and IPv6 address spaces progresses. The situation is different with firewalls, in which the actual number of installed classification rules depends on security policies of a particular network. Since firewall rule sets are not usually publicly available (because of security reasons), the researchers evaluating 5-tuple-based classification algorithms often use synthetic data sets consisting of thousands or tens of thousands of classification rules [64, 55, 40]. Focusing on SDN-enabled switches in a datacenter, each OpenFlow rule may correspond to an active virtual machine, thus their number may be in the order of tens of thousands [41].

In summary, packet classification algorithms targeting core networks have to be able to classify an incoming packet according to tens or hundreds of bits into tens or hundreds of thousands of classes and provide a new classification result every 6.72 ns. Such requirements on performance prohibit software implementation of packet classification algorithms [19]. Although hardware implementation can be realized using both an ASIC (Application-Specific Integrated Circuit) or an FPGA (Field-Programmable Gate Array), because of its availability, flexibility, and configurability, FPGA-based implementation will be considered further in this thesis. The viability of this approach in an often changing networking environment has also been proved by successful FPGA-based networking platforms: NetCOPE [28] and NetFPGA [68].

#### 2.4.2 Algorithms Benchmarking

The requirements on the performance of packet classification algorithms are continuously increasing, as demonstrated in the previous section. Therefore, the development of classification algorithms that meet these requirements is a never-ending story. To benchmark a new classification algorithm, benchmarking tools (e.g., Netbench [48]) usually assess the following parameters of the algorithm:

- **classification speed** defined as the number of memory accesses required for classification of a single packet;

- memory requirements of a data structure representing a set of classification rules.

In addition, the speed of updates of a classification rule set representation might also be assessed in the course of algorithm's benchmarking.

The practical implementation of a packet classification algorithm has to consider the worst case performance of the algorithm in terms of the above mentioned parameters, but the worst case performance solely depends on a utilized classification rule set. This means that in the ideal case a real rule set is utilized while benchmarking the classification algorithm. Nevertheless, real rule sets are not publicly available for the majority of packet classification use cases (often because of security reasons). One of the few exceptions to this are IPv4/IPv6 prefix sets from forwarding tables of core routers [18, 50], which can be used for benchmarking IP lookup (i.e., the key part of IP routing). However, since IPv6 penetration is expected to grow exponentially in the future and the size of IPv6 forwarding tables depends on the number of allocated IPv6 prefixes, current IPv6 prefix sets cannot be directly used for benchmarking IP lookup algorithms in the future environment.

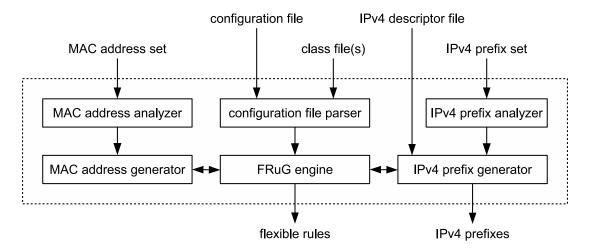

The researchers addressed the issue of missing real benchmarking data in various ways. While a limited number of research groups obtained access to real rule sets via NDAs (*Non-Disclosure Agreements*), others developed several tools capable of generating synthetic data sets for common packet classification use cases. Because the size of IPv4 forwarding tables is not expected to grow significantly in the future, the tools for generating IP prefix sets focus on IPv6 prefix sets only. To get this kind of benchmarking data, it is possible to use for instance Non-random Generator [66] or V6Gene [67]. On the other hand, in the area of 5-tuple rules it makes sense to generate both IPv4 and IPv6 5-tuples. The former is almost exclusively generated using ClassBench [63], while the latter can be generated using ClassBenchv6 [59]. The most problematic is the situation with OpenFlow rules generators. Although FRuG (*Flexible Rule Generator*) [29] is able to generate a set of rules that specify a condition for an arbitrary number of header fields, it does not explicitly consider any specifics of OpenFlow rule sets.

Even though the existing generators are capable of producing IPv4/IPv6 prefixes and 5-tuples as well as rules specifying a condition for more than 5 header fields, none of them explicitly provides support for OpenFlow rules generation. In addition, none of the tools is able to generate all types of benchmarking data, which complicates the situation in case of benchmarking packet classification algorithms targeted at various use cases. Moreover,

it can be shown that the process of rule set generation in available generators is not always accurate. These issues show that packet classification benchmarking is still an open problem.

## Chapter 3

## **Related Work**

While the previous chapter introduced the packet classification operation along with various approaches to its implementation, this chapter contains the selection of already implemented packet classification algorithms and synthetic rule set generators. These algorithms and generators represent current solutions to the performance of packet classification algorithms issue and the packet classification algorithms benchmarking issue, respectively, which were also discussed in the previous chapter. Since the goal of the thesis is to address these issues as well, the algorithms and generators presented in this chapter serve as a starting point for work described in this thesis and they will be used as a baseline for the evaluation of proposed solutions to the identified issues in research on packet classification in core networks.

The first part of this chapter focuses on existing packet classification algorithms, separately for the 1-dimensional and multi-dimensional case. Section 3.1 describes 1-dimensional algorithms, all of which implements the prefix matching approach to packet classification. The reasons for including prefix matching algorithms only are that the prefix specification is utilized in IP lookup (i.e., probably the most common type of packet classification in core networks) and it is also commonly used as a uniform way of specifying all conditions of a classification rule. On the other hand, multi-dimensional algorithms presented in Section 3.2 implement various approaches to packet classification. Actually, a single multi-dimensional algorithm often combines multiple approaches together.

Similarly to packet classification algorithms, synthetic rule set generators, which were already briefly introduced in Section 2.4.2, are also described separately for the 1-dimensional and multi-dimensional case. All 1-dimensional generators presented in Section 3.3 implement the generation of IP prefixes (i.e., classification rules for benchmarking IP lookup). More precisely, they are specialized on generating IPv6 prefixes because currently available real IPv6 prefix sets are not suitable for benchmarking as they are expected to significantly grow in size in the future. The situation is different in case of multi-dimensional generators, which are described in Section 3.4. They primarily support the generation of IPv4 5-tuples, but some of them also allow to generate IPv6 5-tuples or classification rules specifying a condition for more than 5 header fields.

### 3.1 1-Dimensional Packet Classification Algorithms

Probably the most common type of 1-dimensional packet classification in core networks is prefix matching on destination IP address, which is known as IP lookup. Because of its constant matching performance and a direct support of the prefix specification, many commercial devices implement IP lookup using TCAM. However, such implementation suffers from high power consumption, high cost per bit, storage inefficiency, and limited scalability, which makes also algorithmic solutions to prefix matching a viable option for IP lookup implementation [51]. Although prefix matching algorithms employ various approaches (e.g., hashing), the majority of them encode a prefix set using a binary prefix tree that is usually called trie. Therefore, this section presents selected trie-based prefix matching algorithms.

Individual prefix matching algorithms are illustrated on the set of *address* prefixes from the example rule set introduced in Table 2.2. Table 3.1 shows this prefix set sorted from the shortest to the longest prefix.

| Prefix | Value    |

|--------|----------|

| P1     | *        |

| P2     | $0^{*}$  |

| P3     | $11^{*}$ |

| P4     | 010      |

Table 3.1: The set of *address* prefixes from the example rule set (Table 2.2) sorted from the shortest to the longest prefix.

#### 3.1.1 Trie

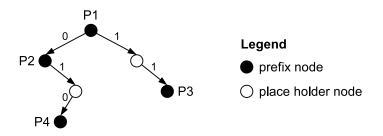

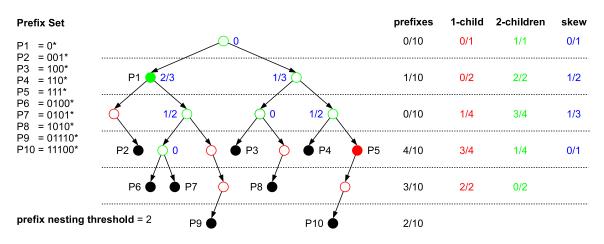

The trie data structure, which has been proposed by Fredkin [27], represents the basis of prefix set encoding in the majority of prefix matching algorithms. It is a binary prefix tree in which each node represents a prefix. The root node represents the empty prefix and left and right child nodes of any trie node represent prefixes created from their parent's prefix by appending 0 and 1, respectively. Trie nodes representing prefixes from a prefix set are called prefix nodes, while other trie nodes are referred to as place holder nodes. The representation of the prefix set from Table 3.1 using a trie is shown in Figure 3.1.

Figure 3.1: The representation of the prefix set from Table 3.1 using a trie.

Matching prefixes of a prefix set represented by a trie is done by traversing the trie from the root to the leaves according to the bits of an input value (e.g., a destination address in case of IP lookup) taken from the MSB (*Most Significant Bit*) to LSB (*Least Significant Bit*). All prefix nodes visited during such a traversal represent prefixes matching the input value and the last visited prefix node represents the longest matching prefix, which is the output of the LPM operation.

Since a trie is a binary prefix tree, the implementation of prefix matching based on a trie is straightforward because operations on a trie (adding, removing, or matching prefixes)

can be realized using standard operations on a binary tree. However, a trie allows to match only one bit of the input value in each step, which means linear time complexity with respect to the bit width of an input value. Therefore, in the worst case it is necessary to perform 32 and 128 steps for matching a full IPv4 and IPv6 prefix, respectively. Due to the high number of pointers in a trie, this data structure also suffers from high memory requirements.

In order to diminish the main disadvantage of a trie (i.e., matching only one input bit in each step), modern trie-based prefix matching algorithms employ the concept of so called multibit trie. These algorithms propose new types of node that represent subtrees of a trie and allow to match multiple bits per step. Thus, although a trie is not directly applicable for high-performance prefix matching, it is a seminal data structure for modern prefix matching algorithms.

#### 3.1.2 Tree Bitmap

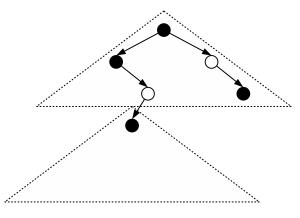

Tree Bitmap (TBM), which has been developed by Eatherton, Varghese, and Dittia [26], is one of the best known multibit trie algorithms. It represents a set of prefixes using a  $2^{SL}$ -tree, where parameter SL (stride length) determines the number of input bits matched in each step. This tree is built on the top of a trie by mapping TBM nodes, each of which corresponds to trie's subtree of the maximum depth equal to SL, onto the trie in a non-overlapping fashion such that each trie node is covered by a TBM node. An example of the mapping of TBM nodes with SL = 3 onto the trie from Figure 3.1 is shown in Figure 3.2.

Figure 3.2: The mapping of TBM nodes with SL = 3 onto the trie representing the prefix set from Table 3.1.

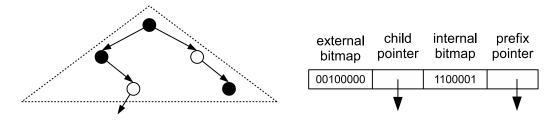

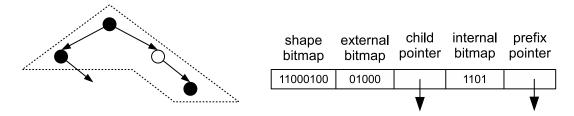

The details of TBM node's encoding are illustrated in Figure 3.3 that shows the root TBM node from Figure 3.2 and its encoding using two bitmaps and two pointers. The external bitmap contains  $2^{SL}$  bits determining whether a corresponding child node is present (value 1) or missing (value 0). Note that MSB of the external bitmap corresponds to the leftmost child, while its LSB corresponds to the rightmost child. On the other hand,  $2^{SL} - 1$  bits of the internal bitmap correspond to the nodes of the underlying trie in breadth-first order and each bit encodes information whether a corresponding internal node is a prefix node (value 1) or non-prefix node (value 0).

The child and prefix pointers refer to information about child nodes and prefix-related data, respectively. In order to minimize the size of the TBM node's data structure and speed up its retrieving from a memory, these information are stored outside the node itself.

Figure 3.3: The encoding of the root TBM node from Figure 3.2.

Nevertheless, both types of externally stored information are in a continuous block of the memory and they are stored in the same order in which they appear in the corresponding bitmaps. Such organization allows to use pointer arithmetic to directly retrieve information about any child node or prefix-related data using just the corresponding pointer and bitmap (the child pointer and external bitmap in case of information about child nodes, the prefix pointer and internal bitmap in case of prefix-related data).

The compact representation of a TBM node makes possible to retrieve it from a memory in just one clock cycle. Additionally, due to the use of bitmaps for node's encoding, this prefix matching algorithm is easily implementable in hardware. The TBM algorithm is thus able to achieve high matching performance. In addition, the fixed structure of a node allows easy updates of the represented prefix set. However, it may also cause high memory overhead when the underlying trie is sparse. Trade-off between matching performance and memory requirements of the TBM algorithm for a given prefix set can be tuned via parameter SL. Clearly, a higher value of parameter SL results in a lower number of matching steps but higher memory overhead and vice versa.

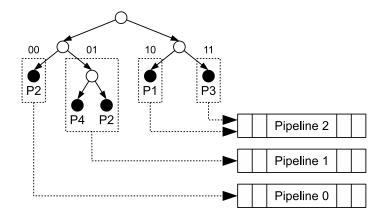

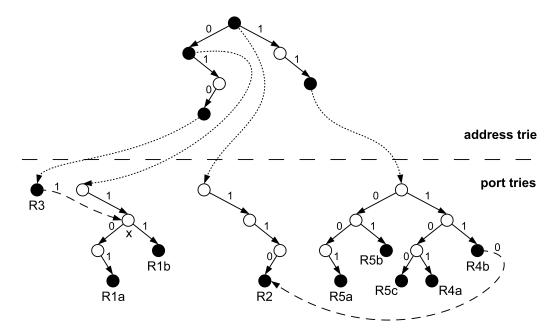

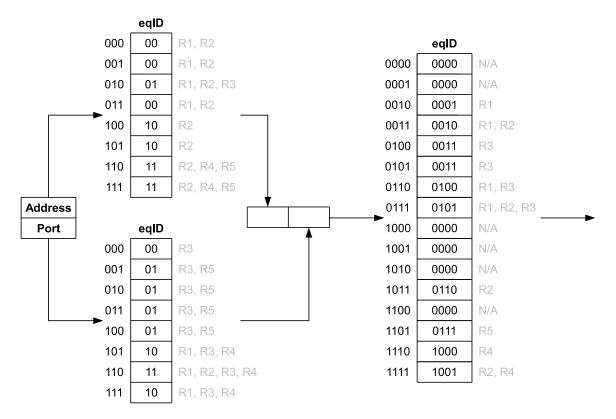

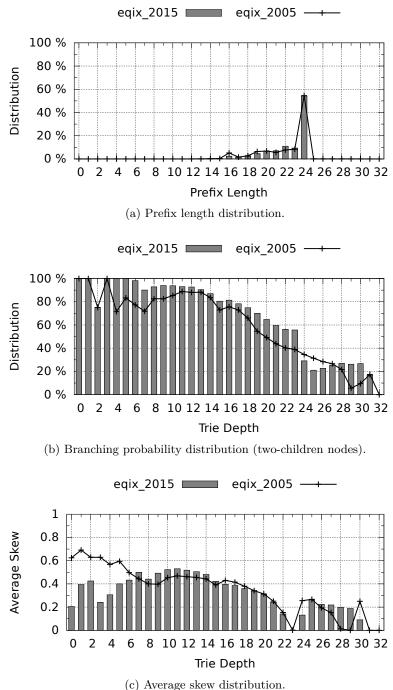

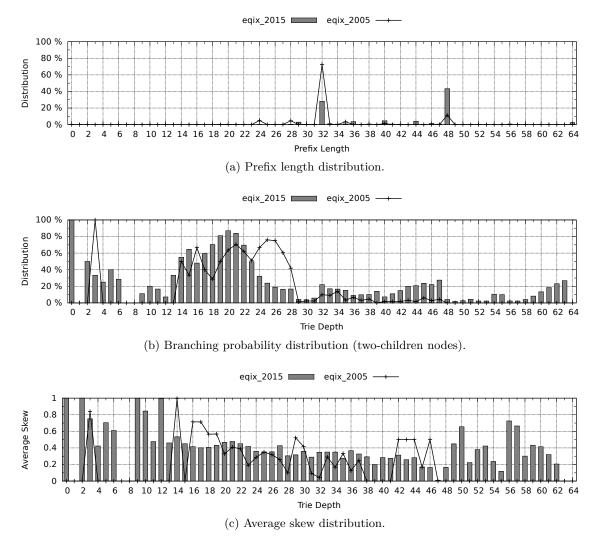

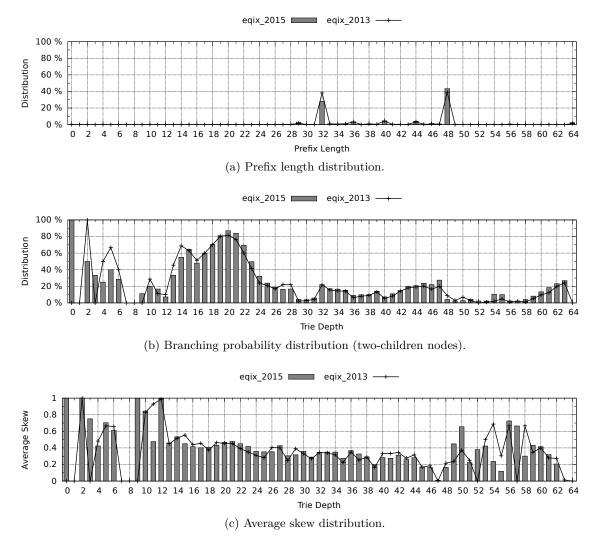

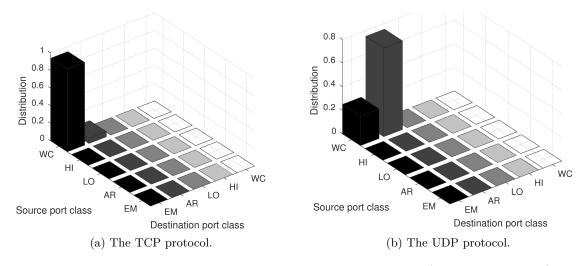

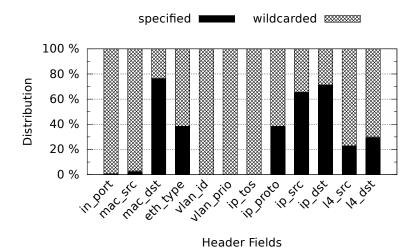

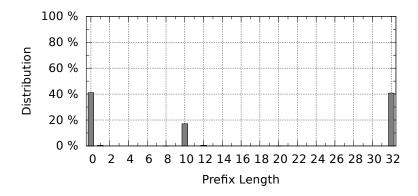

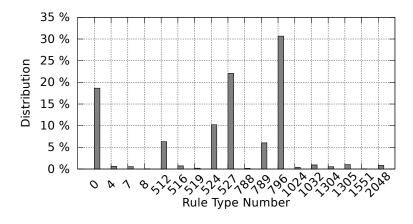

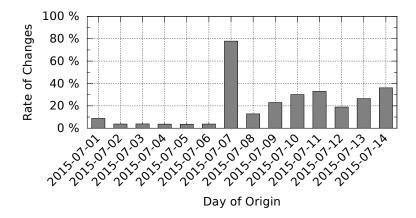

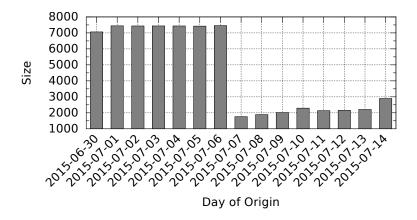

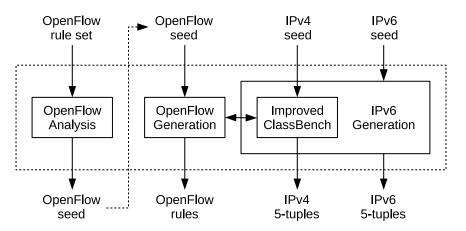

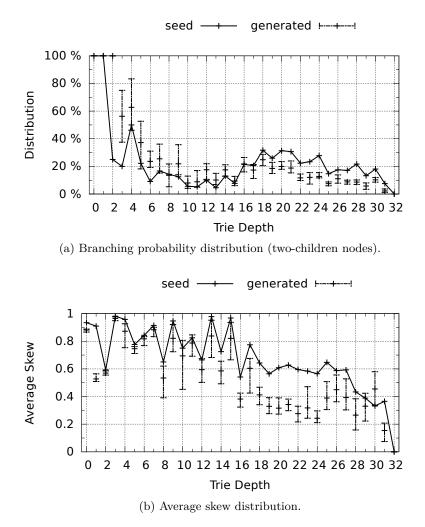

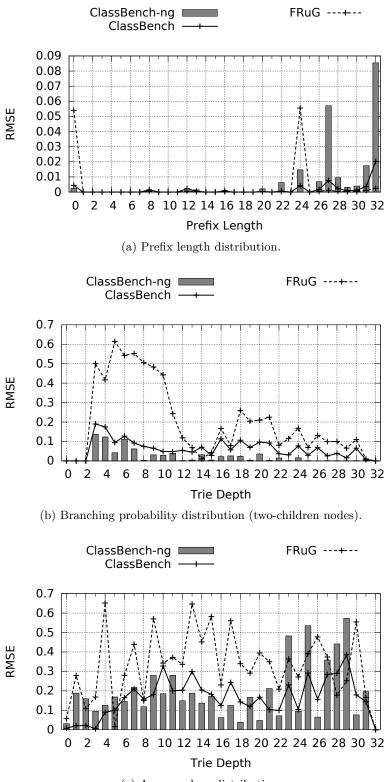

#### 3.1.3 Shape Shifting Trie