### **BRNO UNIVERSITY OF TECHNOLOGY** VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

FACULTY OF INFORMATION TECHNOLOGY FAKULTA INFORMAČNÍCH TECHNOLOGIÍ

DEPARTMENT OF COMPUTER SYSTEMS ÚSTAV POČÍTAČOVÝCH SYSTÉMŮ

# POLYMORPHIC CIRCUITS SYNTHESIS AND OPTIMIZATION

SYNTÉZA A OPTIMALIZACE POLYMORFNÍCH OBVODŮ

PHD THESIS DISERTAČNÍ PRÁCE

AUTHOR AUTOR PRÁCE Ing. ADAM CRHA

SUPERVISOR ŠKOLITEL Doc. Ing. RICHARD RŮŽIČKA, Ph.D. MBA.

**BRNO 2020**

## Abstract

This thesis deals with synthesis and optimization methods of polymorphic circuits. Ordinary and multi-functional synthesis and optimization methods are discussed. The main objective of this thesis is to introduce novel methodologies for scalable synthesis of multifunctional digital circuits. Despite the fact that several approaches have been proposed during recent years, those are applicable for small-scale circuits only or are based on various evolution-inspired techniques. Obviously, scalable synthesis methodology for complex multi-functional circuits does not exist yet. The proposed methodology is based on And-Inverter Graphs (AIGs) with built-in extension for multi-functional circuits where the employment of rewriting techniques reduces the area by sharing common resources of two different input circuits. Experiments performed on publicly available benchmark circuits demonstrate significant optimization achievements.

## Abstrakt

Tato práce se zabývá metodami logické syntézy a optimalizací pro polymorfní obvody. V práci jsou jak diskutovány existující metody pro konvenční obvody, tak i představeny nové metody, aplikovatelné na polymorfní elektroniku. Hlavním přínosem práce je představení nových metod optimalizace a logické syntézy pro polymorfní obvody. Přesto, že v minulých letech byly představeny metody pro návrh polymorfních obvodů, jsou tyto metody založené na evolučních technikách nebo nejsou dobře škálovatelné. Z toho vyplývá, že stále neexistuje stabilní metodika pro návrh složitějších polymorfních obvodů. Tato práce představuje zejména reprezentaci polymorgních obvodů a metodiku pro jejich návrh založenou na And-Inverter grafech. Na polymorfní obvody reprezentované pomocí AIG je možné aplikovat známé techniky jako například přepisování [rewriting]. Nasazením techniky přepisování na polymorfní AIG získáme obvod, obsahující polymorfní prvky uvnitř obvodu, a je možné dosáhnout značných úspor prostředků, které mohou být sdíleny mezi dvěma funkcemi současně. Ověření návrhové metodiky pro polymorfní obvody bylo provedeno nad sadou veřejně dostupných obvodů, čímž je demonstrována efektivita metodiky.

## Keywords

Polymorphic electronics, polymorphic circuit, logic synthesis, logic optimizations, AIG, PAIG.

## Klíčová slova

Polymorfní elektronika, polymorfní obvod, syntéza číslicových obvodů, optimalizace číslicových obvodů, AIG, PAIG.

## Reference

CRHA, Adam. *Polymorphic circuits* synthesis and optimization. Brno, 2020. PhD thesis. Brno University of Technology, Faculty of Information Technology. Supervisor Doc. Ing. Richard Růžička, Ph.D. MBA.

## Rozšířený abstrakt

Rozvoj číslicové techniky v šedesátých letech minulého století otevíral vědě nový, neprozkoumaný prostor. Nová technologie nabízela nové otázky, na které nebyly známé odpovědi a bylo nutné poznávat a pozorovat chování nových materiálů, ze kterých byla vyrobena logická hradla. S rostoucí integrací byly také kladeny požadavky na vhodné nástroje, pomocí kterých se z hradel navrhovaly složitější číslicové obvody. Nyní, po více než 60 letech existence číslicových obvodů, lze předpokládat existenci efektivních návrhových nástrojů, jejichž vývoj se stabilizoval a dnes už nedochází k tak bouřlivému rozvoji, jako v počátcích číslicové techniky.

Ano, toto tvrzení je zcela pravdivé, hovoříme-li o běžných číslicových obvodech. Avšak v roce 2001 představil A. Stoica moderní pojem "polymorfní elektronika", čímž otevřel další nepříliš prozkoumanou vědeckou oblast [106]. Jde o vícefunkční číslicové obvody, u kterých změna funkce není vyvolána přepínačem nebo rekonfigurací, jak je tomu známo u konvenční elektroniky. Namísto toho je změna funkce vyvolána uvnitř číslicového obvodu v závislosti na externím prostředí (teplota, světlo, ...) [105]. Objev polymorfní elektroniky s sebou přinesl nové technologie a otázky týkající se efektivního návrhu polymorfních obvodů.

Materiály, které dříve byly považovány za nestabilní a tudíž nepoužitelné, nacházejí uplatnění právě v polymorfní elektronice. Je možné sledovat značný pokrok ve vývoji grafenu, křemíkových nanotrubiček a organických materiálů [85] [73]. Jedná se tak o velmi mladou věděckou disciplínu nabízející mnoho disertabilních témat.

Bohužel, konvenční návrhové metody a algoritmy nejsou dobře použitelné pro návrh polymorfních obvodů. Metody syntézy pro návrh polymorfních obvodů jsou mnohem složitější než metody syntézy konvenční elektroniky. Touto problematikou se již zabývalo několik výzkumníku, avšak dosud objevené syntézní metody nejsou natolik efektivní jako metody pro návrh konvenční elektroniky. Tato situace vyžaduje výzkum a vývoj nových, lepších a efektivnějších návrhových metod pro polymorfní obvody. Největší přínos polymorfní elektroniky je spatřován ve sdílení prostředků realizovaných funkcí v co největší možné míře. Je snahou objevovat metody, které budou generovat polymorfní obvody splňující tento předpoklad. Syntézní algoritmy pracují s obvody, nejčastěji reprezentovanými pravdivostní tabulkou, logickým výrazem, či binárním rozhodovacím diagramem. Výstupem by měla být co nejjednodušší reprezentace obvodu.

Cílem této práce je obecně představit polymorfní elektroniku a její otevřené problémy (kap. 4), návrhové techniky konvenčních obvodů (kap. 2) a současné návrhové techniky polymorfních obvodů (kap. 5). Práce představuje tři techniky sloužící k návrhu polymorfních obvodů (kap. 7 a kap. 6).

Jedním z hlavních přínosů práce je představení nové reprezentace polymorfních obvodů PAIG, díky které je možné reprezentovat polymorfní obvody v And-Inverter grafu. Na tuto novou reprezentaci je možné aplikovat již existující optimalizační metody, známé jako strukturální hashování či přepisování [rewriting], ale i další. Právě rewriting byl přizpůsoben tak, aby jej bylo možné spustit na reprezentaci PAIG za účelem optimalizace výsledného polymorfního obvodu a propagace polymorfních prvků do nitra obvodu. Práce prezentuje výsledky vykazující efektivitu metodiky a navrhuje další rozšíření.

## Polymorphic circuits synthesis and optimization

## Declaration

I declare that this thesis was prepared as an original author's work under the supervision of doc. Richard Růžička Ph.D., MBA. I declare that all relevant information sources used for this thesis are properly cited.

Adam Crha July 15, 2020

## Acknowledgements

I would like to thank doc. Ing. Richard Růžička, Ph.D., MBA for his support and supervision of this thesis. Next, I would like to thank Ing. Václav Šimek for collaboration on publication activities. Big thanks belongs to my wife Tereza, who supported me, although I have been spending evenings with research instead of spending evenings with her. I'm thanking to my parents who supported me during whole Ph.D. study and also to my cousin, Luděk Bryan, who has been motivating me not only during Ph.D. study.

# Contents

| <b>1</b> | Intr | oducti  | ion                                             | 4  |

|----------|------|---------|-------------------------------------------------|----|

|          | 1.1  | Resear  | rch motivation                                  | 4  |

|          | 1.2  | Thesis  | organization                                    | 5  |

|          | 1.3  | Digita  | l circuits design background                    | 5  |

|          |      | 1.3.1   | Logic synthesis and optimization                | 7  |

| <b>2</b> | Ove  | erview  | of optimization methods                         | 10 |

|          | 2.1  | Optim   | nization metrics                                | 10 |

|          | 2.2  | Descri  | ption of logic circuits                         | 11 |

|          | 2.3  | Two-le  | evel optimization                               | 12 |

|          |      | 2.3.1   | Boolean function representation                 | 12 |

|          |      | 2.3.2   | Karnaugh maps                                   | 12 |

|          |      | 2.3.3   | Quine-McCluskey                                 | 13 |

|          |      | 2.3.4   | Espresso                                        | 13 |

|          |      | 2.3.5   | BOOM - Boolean minimizer                        | 14 |

|          | 2.4  | Multi-  | level optimization                              | 14 |

|          |      | 2.4.1   | Boolean division                                | 15 |

|          |      | 2.4.2   | Binary Decision Diagrams                        | 16 |

|          |      | 2.4.3   | Ordered Binary Decision Diagram (OBDD)          | 16 |

|          |      | 2.4.4   | Reduced Ordered Binary Decision Diagram (ROBDD) | 17 |

|          |      | 2.4.5   | Multi-terminal Binary Decision Diagram (MTBDD)  | 17 |

|          |      | 2.4.6   | And-Inverter graphs                             | 17 |

|          |      | 2.4.7   | Majority-Inverter graphs                        | 17 |

|          |      | 2.4.8   | MIG Boolean algebra                             | 18 |

|          |      | 2.4.9   | MIG optimization                                | 19 |

| 3        | And  | d-Inver | rter Graphs                                     | 20 |

|          | 3.1  | AIG C   | Optimizations                                   | 22 |

|          |      | 3.1.1   | AIG Cuts                                        | 22 |

|          |      | 3.1.2   | Structural hashing                              | 26 |

|          |      | 3.1.3   | Balancing                                       | 26 |

|          |      | 3.1.4   | Refactoring                                     | 26 |

|          |      | 3.1.5   | Resubstitution                                  | 26 |

|          |      | 3.1.6   | Rewriting                                       | 27 |

| 4        | Intr | oducti  | ion to polymorphic electronics                  | 30 |

|          | 4.1  |         | cation scenarios                                | 31 |

|          | 4.2  | ~ ~     | orphic circuits                                 | 33 |

|          | 9.1      | Thesis contribution                                                                                    | 86                                      |

|----------|----------|--------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 9        | Cor      | nclusion                                                                                               | 86                                      |

|          | 8.4      | Comparison of PAIG rewriting to PolyBDD                                                                | 84                                      |

|          | 0.4      | 8.3.3 Related summary                                                                                  | 84                                      |

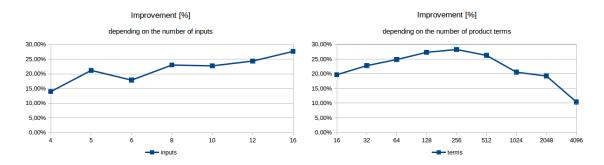

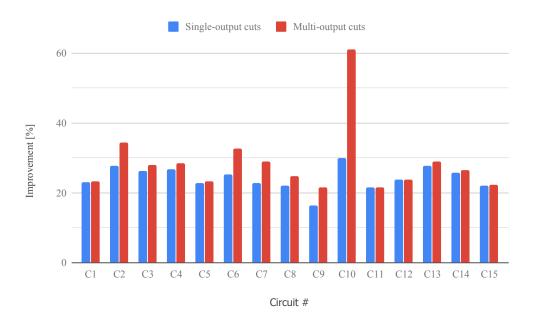

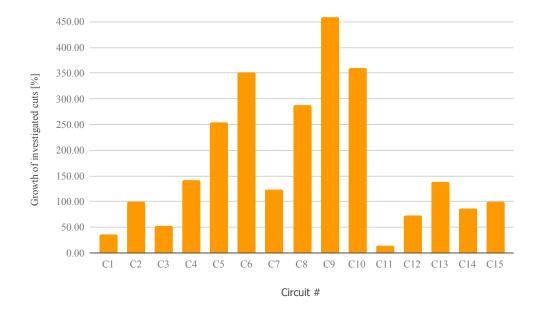

|          |          | 8.3.2 Results analysis                                                                                 | 81                                      |

|          |          | 8.3.1 Specification of benchmark set                                                                   | 80                                      |

|          | 8.3      | KL-cuts influence on PAIG rewriting                                                                    | 80                                      |

|          |          | 8.2.2 Results analysis                                                                                 | 76                                      |

|          |          | 8.2.1 Specification of benchmark set                                                                   | 76                                      |

|          | 8.2      | Switching between two different functions                                                              | 76                                      |

|          |          | 8.1.2 Results analysis                                                                                 | 73                                      |

|          |          | 8.1.1 Specification of benchmark set                                                                   | 72                                      |

|          | 8.1      | Conversion of primary input to virtual polymorphic input                                               | 71                                      |

| 8        | Eva      | luation of multi-level polymorphic design and optimization method                                      | 71                                      |

|          |          |                                                                                                        | 70                                      |

|          |          | 7.2.4 Cut replacing                                                                                    | 08<br>70                                |

|          |          | <ul><li>7.2.2 Cut enumeration in PAIG</li></ul>                                                        | $\begin{array}{c} 68 \\ 68 \end{array}$ |

|          |          | 7.2.1 PAIG rewriting algorithm                                                                         | 66                                      |

|          | 7.2      | Polymorphic AIG Rewriting                                                                              | 65<br>66                                |

|          |          | 7.1.6 PAIG extension summary                                                                           | 65                                      |

|          |          | 7.1.5 Experiments and demonstration                                                                    | 61                                      |

|          |          | 7.1.4 New constructions offered by PAIG extension                                                      | 60                                      |

|          |          | 7.1.3 Newly proposed AIG format for polymorphic circuits: PAIG                                         | 58                                      |

|          |          | 7.1.2 Toolset for operations with AIGs                                                                 | 57                                      |

|          |          | 7.1.1 Elements of And-Inverter Graph scheme                                                            | 56                                      |

|          | 7.1      | PAIG - An extension of AIG for polymorphic circuits                                                    | 56                                      |

| 7        |          | posed multi-level design and optimization method                                                       | 55                                      |

|          |          |                                                                                                        |                                         |

|          |          | 6.2.3 Related summary                                                                                  | 53                                      |

|          |          | 6.2.2 Experiments with MCNC benchmark circuits                                                         | 53                                      |

|          |          | 6.2.1 Experiments with generated circuits                                                              | 51                                      |

|          | 6.2      | Optimization of polymorphic circuits by searching common parts                                         | 49                                      |

|          |          | 6.1.2       Related summary                                                                            | 48                                      |

|          | 0.1      | 6.1.1 Examples                                                                                         | 40<br>47                                |

| 0        | 6.1      | posed two-level design and optimization methods<br>Design of polymorphic circuits using NAND/NOR Gates | <b>4</b> 5                              |

| 6        | <b>D</b> | proceed two lovel design and entimization methods                                                      | 45                                      |

|          |          | 5.1.5 Recent work on logic synthesis of polymorphic circuits                                           | 43                                      |

|          |          | 5.1.4 PolyBDD                                                                                          | 42                                      |

|          |          | 5.1.3 Polymorphic multiplexing                                                                         | 42                                      |

|          |          | 5.1.2 Evolutionary design                                                                              | 41                                      |

|          |          | 5.1.1 Ad - hoc: common sense design                                                                    | 41                                      |

|          | 5.1      | Existing polymorphic design and optimization methods                                                   | 40                                      |

| <b>5</b> | Pol      | ymorphic circuit synthesis and optimization                                                            | 40                                      |

|          |          | 4.2.2 Open issues of polymorphic electronics                                                           | 39                                      |

|          |          |                                                                                                        | $\frac{54}{39}$                         |

|          |          | 4.2.1 Polymorphic logic gates                                                                          | 34                                      |

| 9.2     | Future work | <br>• • | <br> | • | <br>• • | • | <br>• | <br>• | • | ••• | · | <br>• | • | • • | <br> | • | • |   | 87 |

|---------|-------------|---------|------|---|---------|---|-------|-------|---|-----|---|-------|---|-----|------|---|---|---|----|

| Bibliog | graphy      |         |      |   |         |   |       |       |   |     |   |       |   |     |      |   |   | ę | 92 |

# Chapter 1

# Introduction

Reconfigurability as a phenomenon in the world of digital circuits brings more efficient ways to implement certain applications, opens new possibilities and also allows new applications of electronics. As a matter of fact, it makes hardware more flexible. Flexibility is one of the features that make software so popular as a way to implement various systems. But a wide range of applications still needs to be implemented in hardware. So the hardware reconfiguration is (and will be henceforward) very important for significant number of applications.

Typical implementation of the hardware reconfiguration consists of a field of reconfigurable elements, a controller, and memory that serves as a storage for different configurations [10]. The field of reconfigurable elements usually assumes various granularity levels from coarse-grained elements like functional units or data processing units on RT level to transistor-level fine-grained field of elements. This allows not only the classic reconfiguration scheme (the hardware changes its structure and behavior according to the configurations prepared beforehand), but also effective implementation of so-called evolvable hardware (new configurations are being created as a direct response to actual circumstances) [62].

Another (and quite different) concept of hardware reconfiguration was proposed by Stoica et al. under the term "Polymorphic Electronics" [106]. In this concept polymorphic circuits have a permanent structure (interconnections are fixed) and each element (or selected group of elements) of the circuit is sensitive to certain environmental factors (temperature, variation of supply voltage, etc.). Then, the function of a polymorphic circuit changes instantaneously in accordance with those specific factors. If these elements are efficiently implemented and the synthesis of the circuit is properly done, the resulting circuit will be highly efficient. Let me also note that due to the multi-functional nature of individual elements, synthesis of polymorphic circuits is much more complex than synthesis of an ordinary digital circuit.

#### 1.1 Research motivation

It is possible to identify two main issues, which still significantly hinder more extensive adoption of polymorphic electronics as a technique for reconfigurable circuits. The first one results from a lack of suitable polymorphic components on all levels of synthesis. As the majority of polymorphic circuits have been designed on a gate level, the most-wanted polymorphic components are naturally polymorphic gates. Several useful polymorphic gates were proposed during the last decade [90] and some prospective sets of multi-functional gates are emerging even today [77]. The second issue is dealing with multi-functional circuit synthesis using those polymorphic components. As the problem of polymorphic circuit synthesis is relatively hard to address in a conventional way, many of the previously devised polymorphic circuits have been synthesized using evolutionary principles (EA, CGP etc.). Time needed to evolve a result grows dramatically with complexity of a circuit and probability of obtaining reasonable and efficient implementation drops at the same time.

#### 1.2 Thesis organization

Brief introduction to digital circuit design is reviewed in the following section 1.3. The section explains integrated circuits design flow from system specification to physical device. The design flow is demonstrated on a well known Y-chart, where logic synthesis phase takes place. Consequently, the logic synthesis phase is discussed.

Chapter 2 presents existing methods and principles of ordinary logic synthesis and optimization algorithms. Metrics and other terms, that are used further in this thesis, are established. Two-level and multi-level methods are discussed. Subsequently, And-Inverter Graphs, a key scheme of the thesis, is analyzed in detail in chapter 3.

A term polymorphic electronics is first mentioned in chapter 4. The chapter describes evolution of polymorphic electronics and current situation in the field since its introduction in 2001. Principles, ideas and manufacture of polymorphic electronics are discussed, together with application scenarios and open issues. Chapter 5 describes state of the art of currently known synthesis methods for polymorphic circuits.

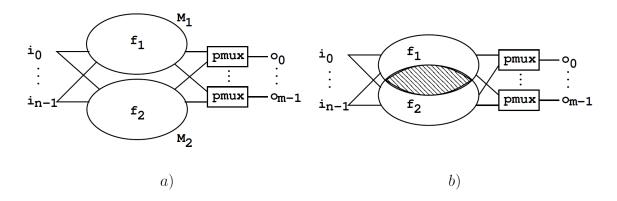

Next chapter 6 describes proposed two-level synthesis and optimization methods for polymorphic circuits. The first mentioned method is based on boolean algebra optimizations in order to design polymorphic circuit having NAND/NOR polymorphic gates (section 6.1). The second method is suitable for detection of common parts in logic expression and thus finding differences in a desired polymorphic circuit (section 6.2).

The main contribution of this thesis is presented in chapter 7. In the beginning, a novel, multi-level representation for polymorphic circuits is introduced. The innovative representation is an extension of AIG, in order to add capability to handle polymorphic circuits. The chapter continues with a proposal of polymorphic-AIG (PAIG) rewriting of polymorphic circuits. Its aim is to optimize a PAIG network.

Major experiments related to PAIG rewriting are described in chapter 8 in detail. The chapter consists of four sections, where the first (section 8.1) optimizes one desired circuit with polymorphic behavior. The second section (section 8.2) focuses on optimization of two independent circuits in polymorphic mode. The second experiment The third experiment (section 8.3) compares PAIG rewriting that allows KL-cuts to PAIG rewriting which permits K-cuts only. The last one (section 8.4) compares the PAIG rewriting with the most famous synthesis method PolyBDD.

Conclusion, thesis contributions and suggestions for future research are discussed in chapter 9.

#### 1.3 Digital circuits design background

In general, an electronic device is a composition of basic electronic components such as resistors, capacitors, inductors, diodes, and transistors interconnected with wires. Interconnection of mentioned components with wires creates an electronic circuit with an ability to perform simple or complex operations such as computation, signal amplifying, data transfer, etc. Electronics can be divided into these groups: digital electronics, analog electronics and mixed electronics, which is mix of both previously mentioned [3].

Digital electronics is a subset of electronics, that operates on digital signals. A highlight of digital electronics in comparison to analog electronics is that digital signals can be transmitted without degradation caused by noise. For example, it is possible to reconstruct an audio signal transmitted as a sequence of ones and zeros without any damage, assuming that noise is not strong enough to prevent recognition of the zeros and ones in the sequence [46]

Electrical signals appearing in digital circuits are discrete and represent logic values. These values represent information that is usually further processed. In most of cases, binary logic is applied: One voltage level (typically positive value) represents logical '1', another voltage level (usually zero voltage) represents logical '0'. Digital circuits are built from logic gates (gates are built from transistors usually) and these gates offer functions of boolean algebra, such as AND, NAND, OR, NOR, XOR, XNOR etc. Combination and interconnection of these elementary gates can represent combinatorial digital circuit. [45]

Digital circuits can be divided in two groups: combinatorial and sequential circuits. Outputs of combinatorial digital circuits depend on and only on values attached to circuit inputs. Sequential digital circuits compute an output value based on values attached to circuit inputs and also on internal state of the sequential circuit. It suggests, the sequential circuits are enriched with memory, which can keep an internal state of a sequential circuit. For the purposes of this thesis, only combinatorial circuits will be discussed in the further text.

Nowadays, nearly all the computing machines are internally based on some variant of a digital circuit. From a formal point of view, its composition can be described in a straightforward way through the following definition [92] below, where its depicted as a variant of acyclic graph:

#### Definition 1. Digital circuit

Let K be a set of functional blocks (e.g. logic gates), and let G is an acyclic graph G = (V, E). Then, a digital circuit is  $C = (V, E, \varphi)$ , where

- V is set of nodes (I/O ports of logic gates),

- $E = \{(a, b) | a, b \in V\}$  is a set of edges (interconnections),

- $\varphi$  denotes a projection that assigns to each vertex from V a component from the set  $K, \varphi: V \to K$ .

The definition 1 describes a structural description of a digital circuit on logical level in Y-chart. The term Y-chart is explained a few paragraphs below. The structural description is used for the purposes of this thesis.

In its most simple valid composition, a digital circuit may consist of a single logic gate or similar fundamental element. It's necessary to point out that in a real situation a circuit would be comprised of potentially high number of mutually interconnected logic blocks (or other substantial parts for its flawless operation).

It involves a term VLSI - Very Large Scale Integration, which means a process of creating an integrated circuit by combining millions of logic gates onto a single integrated circuit. VLSI began in the 1970s when integrated circuits were widely expanded, enabling the development of complex semiconductor technologies. It is good to mention that microprocessors and memory chips are created by VLSI process. Before the introduction of VLSI technology, most integrated circuits had a limited set of functions they could perform. An electronic circuit might consist of a CPU, ROM, RAM and other glue logic. VLSI lets integrated circuits designers add all of these into one chip.

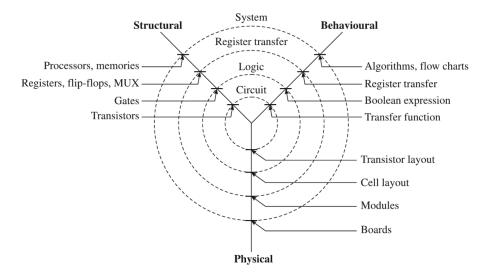

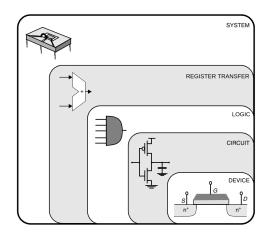

For development of integrated circuits, a Y-chart (also known as Gajski-Kuhn chart) is mostly used. Y-chart was developed in 1983 by Daniel Gajski and Robert Kuhn. The chart, visible in figure 1.1, represents the hardware development view as three domains that are depicted as three axises (behavioral, structural and physical) and looks like an Y. Along these axises, the abstraction levels describe the degree of abstraction. The outer shells are generalizations, the inner ones refinements of the same subject. Abstraction levels are illustrated in a figure 1.2 and also figure 1.1 presents the mentioned Y-chart. The system level describes the most abstract layer, such as processors or SoC's (System-On-Chip). Register Transfer Level describes digital circuits using registers (e.g. adder), logic level works with gates and circuit level operates with transistors.

**Physical axis** binds the structure to silicon. It specifies a Printed Circuit Board (PCB) layout or integrated circuit layout [75].

**Behavioral axis** reflects how a desired circuit should respond to a given input vector. Behavior may be specified by truth tables, Boolean equations, algorithms or any hardware description languages (HDLs) [75].

**Structural axis** describes how components are interconnected to perform a desired function. This representation uses a list of components and their interconnections [75].

The thesis content can be put to logic level, where gates are representatives of structural axis and Boolean expressions of behavioral axis.

Figure 1.1: Y-chart [75].

#### 1.3.1 Logic synthesis and optimization

On the basis given by Y-chart, a design of digital circuits is following the flow from outer shell inwards of Y-chart. To reach a systematic design of VLSI circuits, IC (Integrated circuit) design flow comes out from the Y-chart. IC design flow uses a limited set of

Figure 1.2: Abstraction levels in Y-chart [83].

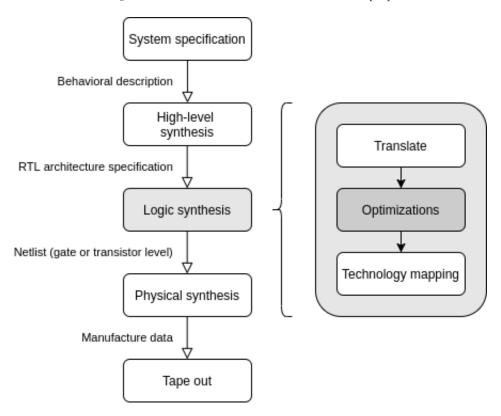

Figure 1.3: Design flow.

digital logic gates (a cell library), and the process can be divided into five parts: System specification, High-Level synthesis, Logic synthesis, Physical synthesis and Tape out.

- *System specification* simply describes the functional and non-functional requirements posed on a system element.

- *High-Level synthesis* makes a transformation at an architectural level, transforming an algorithmic description into an RTL.

- *Logic synthesis* performs a transformation from a behavioral circuit description into a netlist of logic gates of target technology [61].

- *Physical synthesis* (also known as Low-Level Synthesis) is responsible for transformation of a netlist, obtained from logic synthesis, into a set of geometric shapes and layers to be manufactured.

- *Tape out* is the final result of the design process for integrated circuits or printed circuit boards before they are sent for manufacturing.

A design flow is clearly illustrated in figure 1.3. The figure covers all mentioned abstraction layers with processes, that are applied in digital circuit design. The *logic synthesis* block is highlighted and expanded, because the block is essential for this thesis. Logic synthesis flow can be also divided into at least three parts: Translation, optimization and technology mapping:

• Translation

A Register Transfer circuit description is transferred to input format of synthesis tool like PLA (Programmable Logic Array), BLIF (Berkeley Logic Interchange Format), Aiger, etc.

• Optimization

An input is optimized by a synthesis tool. Synthesis tool produces an optimized result/circuit description.

• Technology mapping

An optimized description is mapped onto target technology, where target technology elements are specified by a mapping library. The result is a *Netlist* on the gate level of target technology.

The term **logic synthesis** is a very important topic in EDA (Electronic Design Automation) area [53]. The logic synthesis is a transformation process of a circuit behavioral description into an optimized gate-level representation, i.e. a netlist of gates for a target technology. Main goals of logic synthesis are optimizations, typically area, delay and power optimizations, where these steps are common for two-level and multi-level representations and also for ordinary and multi-functional circuits. The logic synthesis methods attempt to minimize the number of required components, power consumption and delay of signal delivery.

# Chapter 2

# **Overview of optimization methods**

This chapter deals with design and optimization of ordinary combinatorial digital circuits, because the main thesis contribution is logic synthesis and optimization of polymorphic circuits. The most known design and optimization methods are discussed in a following text [119].

Optimization phase clings on optimization methods, which can be categorized into three groups, namely algebraic, graphic and algorithmic.

Algebraic methods take advantage of Boolean algebra laws, where a logic formula is optimized by sequential application of axioms and theorems of Boolean algebra.

Graphical methods are usually based on Boolean neighborhood. A logic function is projected graphically, where an engineer can see particular structures, which can be optimized. For example unit cube, Venn's diagrams, Karnaugh's and Svoboda's maps.

The last kind are algorithmic methods. Algorithmic methods are also based on Boolean neighborhood, but in comparison to graphical methods, it is possible to process optimization by computer. Typical algorithmic methods are Quine McCluskey and Espresso.

#### 2.1 Optimization metrics

The categories of optimization methods has been introduced in the previous section. However, it is appropriate to deploy a quality evaluation of optimized expression. Quality of optimized expressions can be evaluated according to various criteria:

- 1. Size of a circuit: Size of a circuit can be measured as a number of logic gates AND, OR, NOT, ... used in a circuit implementation. The most common gates used in industry are two input NAND gates, which are the most widespread in gate fields.

- 2. Delay of a circuit: Propagation delay or gate delay is the length of time interval which starts when an input to a logic gate becomes stable and valid to change, to the moment that the output of that logic gate is stable and valid to change. Circuit delay is a sum of times of all gates one after another. Circuit delay can affect performance and data propagation through circuit.

- 3. Number of wires: Number of wires can have influence on an area requirements of circuit implementation. Each wire has physical dimensions, resistance and delay.

- 4. **Power:** The last most used criteria is power consumption. Each logic gate requires specific amount of power to work properly. Material and internal construction of logic gates have influences to power consumption of digital circuit.

Some of metrics mentioned above, are technology dependent and thus it is required to have known target technology during optimization. Because polymorphic electronics doesn't have a solid base in technology level, this thesis will use technology independent metrics such as number of gates, that is usable for wide spread of interested parties.

#### 2.2 Description of logic circuits

A logic optimization process is an algorithm. Algorithm is a finite set of instructions to perform a computation on input data. In the case of logic optimizations, an algorithm optimizes a logic circuit given to an algorithm input. Thus, a logic circuit to be optimized (input data) must have an description format that is passed to optimization algorithm and optimization operations are applicable on description well. Such logic circuit can be described in many forms. The first five forms mentions Mr. Wakerly in his publication [119], where it is also possible to find detailed information. The rest of descriptions are mostly used for multi-level representation. The following text lists the most common description of logic functions [119, 42]:

- **Truth table:** For each primary input and primary output exists exactly one column. Input columns reflects state of primary inputs and output colums reflects all of the possible results of the logical operation that the table represents. Each row express one input combination that affects each primary output state.

- **Disjunctive Normal Form:** A logic formula composed of a disjunction of conjuctive clauses. In other words: DNF Boolean function written as a sum of minterms<sup>1</sup> (products). It is also known with these names: Sum of products (SOP) or "OR of AND's".

- **On-set:** List of line numbers of truth table, where function value is logical one. It is a list of truth table rows, where combination of input variables leads to true function value. On-set of f is  $\{x|f(x) = 1 = f^{-1}(1) = f^1\}$ . Denoted by character  $\sum$ .

- Conjuctive Normal Form: A logic formula composed of a conjunction of disjunctive clauses. In other words: CNF is Boolean function written as a product of maxterms<sup>2</sup> (sums). It is also known with these names: Product of Sums (POS) or "AND of OR's".

- Off-set: List of line numbers of truth table, where function value is logical zero. It is a list of truth table rows, where combination of input variables leads to false function value. Off-set of f is  $\{x|f(x) = 0 = f^{-1}(0) = f^0\}$ . Denoted by character  $\Pi$ .

- Algerbraic expression or formula: An algebraic expression is a mathematical notation that is made up of constants and variables <sup>3</sup>, where meaningful relationships are created by using algebraic operations (eg, addition, multiplication) and parentheses.

<sup>&</sup>lt;sup>1</sup> **Minterm**: A minterm is a product of literals. More specifically, if there are n variables,  $x_1, x_2, ..., x_n$ , a minterm is a product  $y_1y_2...y_n$ , where  $y_i$  is  $x_i$  or  $\overline{x_i}$ .

<sup>&</sup>lt;sup>2</sup> **Maxterm**: A maxterm is a sum of literals. More specifically, if there are n variables,  $x_1, x_2, ..., x_n$ , a maxterm is a sum  $y_1 + y_2 + ... + y_n$ , where  $y_i$  is  $x_i$  or  $\overline{x_i}$ . Maxterms are not usually used in practice, it is related to the fact that NAND gates are often used in practice.

<sup>&</sup>lt;sup>3</sup> Variable: Input of Boolean function. Each k - ary Boolean function has k variables  $x_1, ..., x_k$

- **BDD Binary decision diagrams**: Logic function is expressed by directed acyclic graph structures. Explained later in 2.4.2.

- Boolean networks (AIG, MIG, ...): Another variant of directed acyclic graph to represent a logic function. Also explained later in 3.

This list contains the most known representations of logic functions applicable for two-level and also multi-level logic functions. Other representations can exist, just as exist derivatives of listed representations.

#### 2.3 Two-level optimization

Optimization methods can be divided into two groups - two-level optimization and multilevel optimization methods. For two-level circuits are SOP or POS typical representations forms. Widely used implementation (format) for this kind of circuits is *PLA (Programmable Logic Array)*. On the basis of simplicity of the PLA format of a two-level circuits, the optimization tasks are mostly easy to understood. This chapter describes two-level optimization methods of ordinary circuits.

#### 2.3.1 Boolean function representation

A two-level logic function can be described in many forms. The following list states the most used two-level forms (enumerated from listing in section 2.2): *Truth table, Disjunctive Normal Form, Conjunctive Normal Form, On-set, Off-set.*

Two-level methods generate formulas in disjunctive normal form or in conjunctive normal form. In contrast, multi-level optimization methods can handle and generate formulas with deeper immersion, which lead to optimized circuits with a path longer than two gates.

Input of two-level optimization methods is one of the listed representations, i.e. truth table, algebraic/logic formula or any other equal representation. Basic methods use principles of boolean algebra and applying boolean algebra rules as much as possible. For example, such rules are associativity rule, absorption rule, aggressiveness of zero and one, idempotent rule and also deMorgan's rules.

#### 2.3.2 Karnaugh maps

Kaurnaugh map is a graphical method of minimization of Boolean functions. The principal basis is projection of n-dimensional tabular values into two-dimensional map. Then it is possible to extract, by human's pattern recognition capability, a minimal function from the two-dimensional map [49, 115]. This approach also allows identification and elimination of potential race conditions. Input variables, typically taken from a truth table, are ordered with respect to Gray code and inserted into two-dimensional map, where one cell represents exactly one combination of inputs. Cell value represents the corresponding output value. When the map is prepared on the basis of previous description, cells are collected into the largest possible groups containing  $2^n$  cells, where n is a number of variables in a subexpression. Collected group is a cube<sup>4</sup>, thus conjuction of variables in a group. Once a set of cubes is found, a logic sum of them produces a minimized boolean expression.

It is very simple method for minimization of Boolean expression up to 4 variables because of complexity of two-dimensional map. For more variables, a map becomes harder to read

<sup>&</sup>lt;sup>4</sup> Cube: A cube is defined as the AND of a set of literal functions (conjunction of literals).

and orient in a map. Thus, Karnaugh maps are still used for optimization of Boolean expressions, but for resolution of less complex problems or subproblems only.

#### 2.3.3 Quine-McCluskey

The Quine–McCluskey algorithm (or the method of prime implicants) is a method used for minimization of Boolean functions that was developed by Willard V. Quine and improved by Edward J. McCluskey [80, 81, 60]. The Quine–McCluskey algorithm uses the same idea as Karnaugh map, however it is based on a tabular representation in contrast to Karnaugh maps, which uses a graphical representation. The tabular representation allows resolution by computer algorithms and it also produce deterministic way to generate minimized Boolean function. The method can be divided into two steps: The first step is finding all prime implicants of the booelan function. The second step is creation of a prime implicant chart to find the essential prime implicants of the function, as well as other prime implicants that are necessary to cover the function.

Despite the fact that Quine-McCluskey method is more practical for handling with more than four input variables in comparison to Karnaugh maps, the Quine-McCluskey algorithm has also a limited range of use since the resolution complexity is NP-complete [114]. The resolution time of Quine-McCluskey algorithm grows exponentially with number of input variables.

#### 2.3.4 Espresso

All previously mentioned methods can be considered as basic and exact methods. Methods produce minimal solutions, but most minimization tasks are too complex to by solved by these exact algorithms. Rather than a search of minimal function, heuristic methods are searching a near minimal solution in acceptable time. Espresso is a basic representative of heuristic methods. The Espresso algorithm follows a completely different approach to minimization than exact methods. It was developed by Brayton et al. at the University of California, Berkeley [13]. In a contrast to previous methods, which expand a logic function into minterms, the algorithm manipulates with "cubes", representing the product terms in the On-set, DC-set<sup>5</sup> and Off-set covers iteratively. Despite the fact that the optimization result is not guaranteed to be the global minimum, in practice this is very closely approximated, while the solution is always free from redundancy. In comparison to other mentioned methods, this one is essentially more efficient, reducing memory usage and computation time by several orders of magnitude.

Espresso algorithm works in three steps:

- Reduce Maximally reduce all cubes, so that a cover is retained.

- Expand Maximally expand all cubes, so that a cover is retained.

- Irredundand cover remove a reduntant cover. Then, repeat these steps to find alternative reduced implicants.

However, despite the success and good results, Espresso is applicable only to circuits up to 100 inputs or outputs. To this weakness aims BOOM - Boolean minimizer.

$<sup>^{5}</sup>$  **DC-set**: List of truth table rows, where combination of input variables does not matter output function.

#### 2.3.5 BOOM - Boolean minimizer

Boolean minimizer (BOOM), introduced by Petr Fišer in 2001 [34], is a two-level minimization algorithm based on a new implicant generation paradigm. In comparison to all the mentioned minimization methods, where the implicants are generated in bottom-up order, the BOOM algorithm uses a top-down ordering. Thus, a dimension of a term is gradually decreased by adding new literals <sup>6</sup>, instead of increasing the dimensionality of implicants by omitting literals from their terms. Boolean Minimizer has an ability to optimize logic functions with thousands variables in reasonable execution time.

#### 2.4 Multi-level optimization

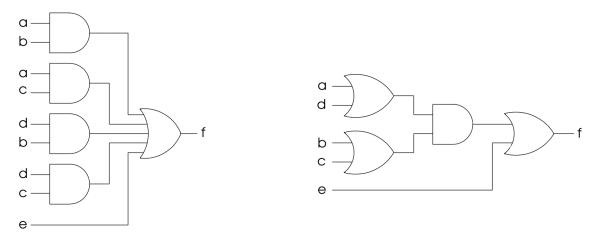

In the real world, computation tasks and requirements for digital circuits are too complex to be covered by two-level circuits. Based on the nature of two-level methods, it is evident that the two-level optimization and synthesis methods are not applicable to complex circuits in a full range. Thus, multi-level optimization and synthesis methods have an irreplaceable position here. Due to complexity of multi-level circuits, truth table or Sum-Of-Products/Products-Of-Sums are not robust enough to describe them, therefore graphical representation and graph operations are most commonly used. The following text and examples are based on these publications [31, 42, 44]. Figure 2.1 shows examples of two-level and multi-level logic circuit.

Figure 2.1: On the left is an example of two-level logic circuit. On the right is an example of multi-level logic circuit. Both performs the same logic function.

For multi-level optimization, five basic operations are widely know, such as:

• *Decomposition:* decomposing a complex Boolean function into elementary gates from a given library. i.e. express a single function by a set of functions. Usage of multiple subexpressions is expected and result need not be in factored form.

**Example 1.**

$$F = abc + abd + \overline{acd} + \overline{bcd} \rightarrow \begin{array}{c} F = XY + \overline{XY} \\ X = ab \\ Y = c + d \end{array}$$

<sup>&</sup>lt;sup>6</sup> Literal: A literal is a Boolean variable or the complement of a Boolean variable. For example  $x_1, \overline{x_1}, x_2, \overline{x_2}$ .

• *Extraction:* expressing a set of functions by a set of functions. Extraction extracts common subexpressions of more functions in comparison to decomposition.

F = ACd + bcd + e F = acd + bcd + e  $G = X\overline{e}$  F = ACd + bcd + e  $G = X\overline{e}$  H = Ye H = cde X = a + b Y = cd

• Factorization (serial-parallel decomposition): Searching factors, that is create a factored form from a SOP.

Example 3.

$$F = abc + abd + \overline{acd} + \overline{bcd} \rightarrow F = ab(c+d) + \overline{cd}(\overline{a} + \overline{b})$$

• Substitution: Express a function using another function.

Example 4.

$$\begin{split} F &= ac + ad + b \overline{c} \overline{d} & F &= Ga + \overline{G} b \\ G &= c + d & \rightarrow & G &= c + d \end{split}$$

• Collapse (eliminate): expressing a function without using another function (opposite of substitution). In other words, express a function using primary inputs only or express a network using a SOP form.

#### Example 5.

$\begin{array}{ll} F = Ga + \overline{G}b & F = ac + ad + b\overline{c}\overline{d} \\ G = c + d & \rightarrow & G = c + d \end{array}$

#### 2.4.1 Boolean division

Previously mentioned operations are a basis for algorithmic optimization. However, the question is how to do all the mentioned operations? Questions "How to find common factors?", "What factor choose? Which factors are the best?" or "How to find shared expressions?" are in right place. As a reader can observe from examples, it is all about searching common subexpressions and it may seem like division by a common divisor. Unfortunately, *"Boolean division"* doesn't exists in Boolean algebra. Nevertheless, it is possible to factor a function into three parts:

$$f = p * q + r$$

where p is a Boolean divisor, q is a quotient and r is a remainder. Thanks to this equation, it is possible to perform boolean division of function f by a divisor p. Thus, the aim is to find functions (quotient) q and remainder r.

In the previous paragraph it has been mentioned that it is possible to perform boolean division of a given function f and a divisor p, but how to find the best divisor p? The answer is: *kerneling*.

Kerneling is a methodology of looking for common subexpressions (divisors) of a given function f. Kernels are divisors p for division of an expression f. Such kernel is a cube-free primary divisor. A cube-free expression is an expression without factors:

#### Example 6.

ab + c is cube free. ab + ac is not cube free (a is a divisor). abc is not cube free (a, b, c are a divisors).

Kerneling plays a key role in all mentioned operations (decomposition, factoring, extraction, substitution), where the best kernel intersections can be used as divisors for boolean division. It is also important to notice that the kerneling and Boolean division are not the only existing methods and other decomposition (Boolean) methods already exist, such as Ashenhurst [8], Curtis [30], Roth and Karp [88], Steinbach [70] or Karplus [50] and others [52, 84], but description of these boolean decomposition methods exceeds the content of this thesis.

For a representation of complex boolean functions, logic formulas are not robust enough and we need something to represent a complex logic network. The following text makes an introduction of existing, well known, multi-level representation and synthesis methods of conventional logic synthesis.

#### 2.4.2 Binary Decision Diagrams

The main idea of Binary decision diagrams (BDDs) had grown from Shannon decomposition, that can be used to split a Boolean function into two simpler subfunctions until the constant functions 0 and 1 are obtained [32].

BDD is a data structure for representation of a Boolean functions introduced by Lee in 1959 [54, 32], where a function is represented by directed acyclic graph (DAG) composed of terminal and decision nodes. BDD can be formally defined as follows 2:

**Definition 2.** Let G = (V, E) is a directed, acyclic graph, where V is a set of nodes and E is set of oriented edges (see definition 1). Then,  $G_{BDD} = (V, E, X)$  is Binary Decision Diagram over set of input variables  $X = \{x_1, \ldots, x_n\}$ , if:

- $G_{BDD}$  has exactly one root  $v \in V$ ,

- each terminal node in V is labeled with a value from  $\{0, 1\}$ ,

- each non-terminal node is labeled with a variable  $x_i \in X_n$  and has exactly two outgoing edges, whose ends are denoted by lhs(v) resp. rhs(v) ( $lhs(v), rhs(v) \in V$ ). Its means , left hand side" and rhs means , right hand side".

Thanks to graph representation of BDDs, many graph operations are applicable to them. The most of operations are feasible in polynomial time  $\mathcal{O}(n^k)$  with respect to input variables, such as conjunction, disjunction and negation.

#### 2.4.3 Ordered Binary Decision Diagram (OBDD)

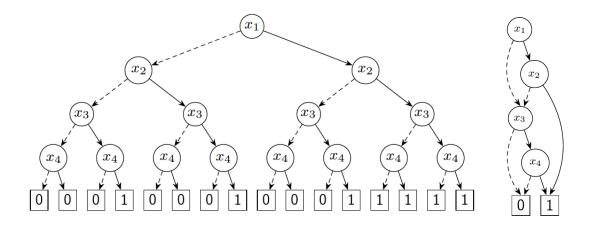

In order to express functions by BDDs more effectively, a few compact variants exist. The first one is Ordered Binary Decision Diagram (OBDD). OBDD has ordered input variables, i.e input variables appear in the same order on all paths from the root node. It is possible to see complete ordered binary decision diagram in figure 2.2 on the left.

Figure 2.2: (OBDD) Complete and ordered binary decision diagram on the left. (ROBDD) Reduced ordered binary decision diagram on the right. Both graphs represents the same function.

#### 2.4.4 Reduced Ordered Binary Decision Diagram (ROBDD)

Reduced Ordered Binary Decision Diagram (ROBDD) is another kind of BDD. Reduced BDD must fulfill two rules:

- All isomorphic subgraphs are merged.

- All nodes, whose children are isomorphic, are eliminated.

The main advantage of ROBDDs is canonicity<sup>7</sup>. This property enables usage in functional equivalence checking and functional technology mapping [14]. ROBDDs are the most commonly used BDDs and if BDD is mentioned, in the most cases ROBDD is meant. ROBDD is shown in figure 2.2 on the right.

#### 2.4.5 Multi-terminal Binary Decision Diagram (MTBDD)

The last kind of BDD, that should be mentioned is Multi-terminal Binary Decision Diagram (MTBDD). Instead of logic zeros and logic ones, terminals can keep other integer values - multivalued logic.

#### 2.4.6 And-Inverter graphs

And-inverter graphs (AIGs) are essential for this thesis and therefore AIGs are described in the next chapter 3 in detail.

#### 2.4.7 Majority-Inverter graphs

Majority-Inverter Graphs (MIGs) are a relatively novel logic representation structure for efficient optimization of Boolean functions. MIGs were introduced by Luca Amarú in 2014 [5] and can be considered the most effective representation of logic functions today (see definition 4).

<sup>&</sup>lt;sup>7</sup> Canonical representation: Representation is unique for a particular function and variable order.

MIG is a directed acyclic graph (DAG) composed of three-input majority nodes and regular/inverted edges.

**Definition 3.** Majority operator is a function M(a, b, c), where a, b, c are input Boolean variables. When a sum of positive logic values is higher than a sum of negative logic values, operator returns true, otherwise false.

**Definition 4.** *MIG is a homogeneous logic network with indegree equal to 3 and with each node representing the majority function (operator). In MIG, edges are marked by a regular or complemented attribute [5].*

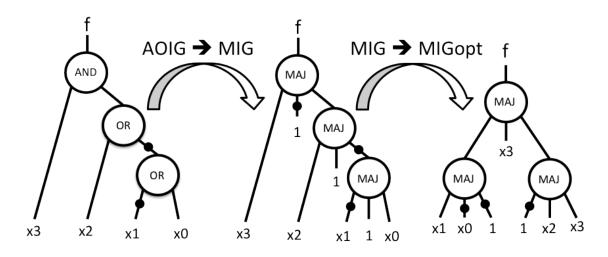

MIGs can be compared with And/Or Inverter Graphs (AOIGs), while MIGs offer a more compact representation for logic. Each AIOG network (optimized network included) can be expressed by MIG network, whereas MIG network can be further optimized. Conversion from AIOGs to MIGs follows from *Majority operator*.

Based on definition 3, if c = 0, majority operator performs AND(a, b) operator, while c = 1 majority operator behaves as OR(a, b) operator. It supports the claim that MIGs can express an arbitrary AIOG, OIG or AIG network:  $MIGs \supset AIOGs \supset AIGs$ , which implies that MIGs are the most universal representation form of all enumerated representations. See figure 2.3 for an example of AIOG conversion into MIG and further MIG optimization. For complete definitions and proofs, please see [5].

Figure 2.3: Example of conversion AOIG network into MIG and further MIG optimization [4].

#### 2.4.8 MIG Boolean algebra

In order to support natural manipulation with MIGs, a new Boolean algebra has been introduced, based exclusively on majority and inverter operations, with a complete axiomatic system. Set of five transformation rules on Majority operator are enumerated [5]:

- 1. Commutativity  $\Omega.C$ M(x, y, z) = M(y, x, z) = M(z, y, x)

- 2. Majority  $\Omega.M$ if(x = y): M(x, y, z) = x = yif(x = y'): M(x, y, z) = z

- 3. Associativity  $\Omega.A$ M(x, u, M(y, u, z)) = M(z, u, M(y, u, x))

- 4. Distributivity  $\Omega.D$ M(x, y, M(u, v, z)) = M(M(x, y, u), M(x, y, v), z)

- 5. Inverter propagation  $\Omega I M'(x, y, z) = M(x', y', z')$

These five primitive transformation are fully sufficient for transformation of any MIG  $\alpha$  into any other logically equivalent MIG  $\beta$ , by sequential application. However, the length of transformation sequence may not be practical for modern computers. To avoid this problem, authors derived another three powerful transformations  $\Psi$  from  $\Omega$ :

- 1. Relevance, replaces and simplifies reconvergent variables  $\Psi.R$   $M(x,y,z) = M(x,y,z_{x/y'})$

- 2. Complementary Associativity, deals with variables appearing in both polarities  $\Psi.C$ M(x, u, M(y, u', z)) = M(x, u, M(y, x, z))

- 3. Substitution, extends variable replacement also in the non-reconvergent case  $\Psi$ . M(x, y, z) = $M(v, M(v', M_{v/u}(x, y, z), u), M(v', M_{v/u'}(x, y, z), u'))$

#### 2.4.9 MIG optimization

The optimization of an MIG, representing a logic function, is a transformation process into different, functionally equivalent MIG, having better quality terms such as size, delay or power consumption. By application of transformation rules from  $\Omega, \Psi$  to an input MIG, it is possible to reduce size, optimize delay or decrease switching activity of an optimized MIG [5].

Another optimization method on MIGs, introduced in [101], consists in functional hashing of MIGs nodes, which is very similar to DAG-aware AIG rewriting (discussed in section 3.1.6) [68], but deployed on MIGs. This approach aims to size reduction of an initial MIG and experiments report remarkable results.

# Chapter 3

# And-Inverter Graphs

The most popular representation of digital circuits structural implementation in the last fifteen years are And-Inverter Graphs (AIGs) definitely. AIGs have found their application primarily in logic synthesis and optimizations. However, the first mention about AIGs we can find in an Alan Turing's paper [48] on neural networks, where he has been writing about randomized trainable network of NAND gates. Since the publication, AIGs had felt into oblivion, a few local transformations have been introduced. AIGs and their local transformations have began to appear in several logic synthesis and verification systems in 1980s, with the aim to reduce circuit area and delay during synthesis process or accelerate formal equivalence checking process [31, 100]. A big progress has been done in IBM by discovering important AIG properties, such as structural hashing. BDDs have been very popular for logic synthesis application in 1990s and thus AIGs have started rising up again around year 2000, when BDDs have reached their scalability boundaries in many of their applications. Interest in AIGs was resumed when AIGs have began to be used as a functional representation for a variety of tasks in synthesis and verification. It has been discovered, that when AIGs are used for circuit representation, a significant acceleration is observed in solving a wide variety of boolean problems.

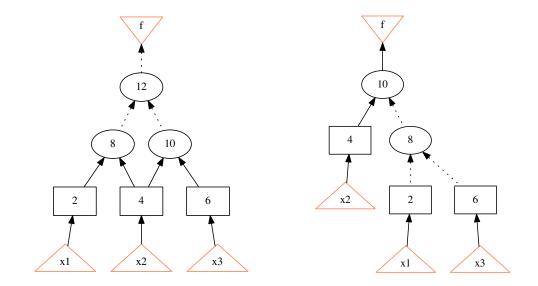

An And-Inverter Graph is a directed acyclic graph for structural representation of Boolean logic circuit. AIG is composed only of two input AND gates and two kind of edges: wire and inverter. Terminals nodes are primary inputs and roots represent primary outputs. AIGs can represent an arbitrary logic function and offers very efficient manipulation of these functions. The following definition 5 supports a formal background of AIGs and figure 3.1 shows an example of AIG network before and after optimization.

**Definition 5.** Let G is a directed acyclic graph G = (V, E). AIG A = (V, E, X, f) is an extension of graph G, where

- $V = X \cup N \cup \{0\}$  is a finite set of nodes, where  $X = \{x_1, ..., x_n\}$  are primary inputs,  $N = \{n_1, ..., n_k\} = V \setminus (X \cup \{0\})$  are non-terminal nodes representing the logic AND operator and 0 is the constant 0 input,

- E = {(a,b)|a ∈ N, b ∈ V} is a set of edges (interconnections), so that every node a ∈ N has exactly two outgoing edges.

- f: E → T, where T = {wire, inverter}, is a function that specifies, whether the edge is a wire or an inverter.

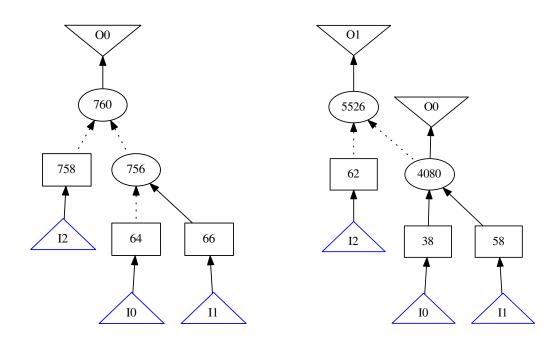

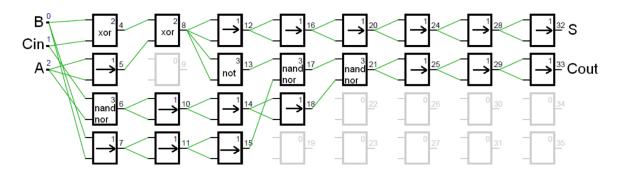

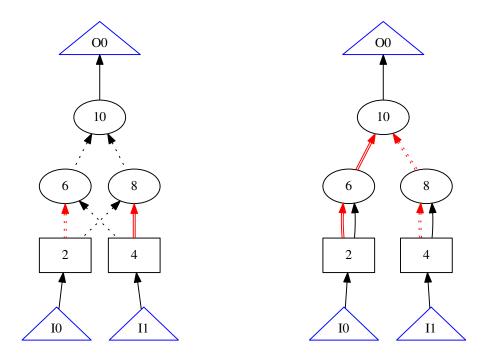

Figure 3.1 represents a convention how AIGs will be shown in this thesis. Each primary input is represented by a triangle and a square at the bottom of the picture, where squares

denote input latch registers. Rounded nodes represent a logic AND gates with 2-indegree numbered with even numbers. Even numbering reflects AIGER format and internal implementation described further in the text 7.1.2. Interconnection between nodes are solid or dotted arrows. Solid arrow represent regular wire and dotted arrows represent inverter in the connection<sup>1</sup>. Primary outputs are recognizable as triangles at the top of the network.

Figure 3.1: Example of AIG network. The network on the left represents function  $f(x_1, x_2, x_3) = x_1x_2 + x_2x_3$ . The network on the right represent a functionally equivalent, but structurally different function  $f(x_1, x_2, x_3) = x_2(x_1 + x_3)$ .

A transformation of an ordinary network, composed of logic gates, into AIG requires only a conversion table of each logic gate, expressed in terms of AND gates and inverters or application of DeMorgan's rules. Simply, to derivate an AIG, factor SOPs of the nodes in a logic network, then AND/OR factored forms convert to 2-indegree AND nodes and inverters by applying DeMorgan's rules. Thus, the transformation is scalable, fast and doesn't lead to unpredictable memory and runtime blowup. It makes the AIG an efficient representation compared to SOP (Sum-Of-Product) form or BDDs (Binary Decision Diagrams) representation (see section 2.4.2). SOP or BDD representations can also be handled as logic circuits, but they impose somewhat artificial constraints, which often deprive them of scalability. SOPs are circuits with at most two-levels and BDDs are canonical, it means, they require that input variables were evaluated in the same order on all paths [64].

AIGs can also represent sequential logic and sequential transformations, using D-flipflops with an initial state. However, the thesis doesn't aim to the sequential circuits, but it can be considered as a future work.

AIG ordinary concept is already implemented in ABC tool [1], which is an academic synthesis tool, developed by Alan Mishchenko at the University of Berkeley. ABC is completely based on AIGs containing AIG-based synthesis and equivalence checking techniques.

<sup>&</sup>lt;sup>1</sup>Graphical representation of edges differs from commonly used notation. Arrows lead from leafs to roots.

#### **3.1** AIG Optimizations

The optimization of an AIG is a transformation of AIG  $\alpha$  into different AIG  $\beta$ , that is functionally equivalent with  $\alpha$ , having better parameter terms, such as area, depth or switching activity. For all mentioned items exist particular optimization techniques, and further research continues.

Logic optimization methods, except graphical methods, may be seen as two groups: Boolean methods and algebraic methods. Algebraic methods handle Boolean function as polynomial expression and thus these methods has limited set of allowed operations (associativity, commutativity and identity) in comparison to Boolean methods (associativity, commutativity, identity, annihilation, distributivity, idempotence, absorption, complementation, De Morgan rule and double negation), which are based on Boolean algebra. It implies, that Boolean methods are more efficient (better optimization results) in comparison to algebraic methods, but they also require more computation time. In order to apply the Boolean methods onto large logic networks, a known practice is to make a Boolean transformation only in a particular subgraph of a large logic network at a time. This approach, namely local optimization, is essential for scalability of many optimization algorithms.

One of the subgraph selection methods is *Windowing*, introduced in [72, 65], which is applicable for local optimizations. The main aim of the windowing algorithm is to collect nodes around a node n.

#### 3.1.1 AIG Cuts

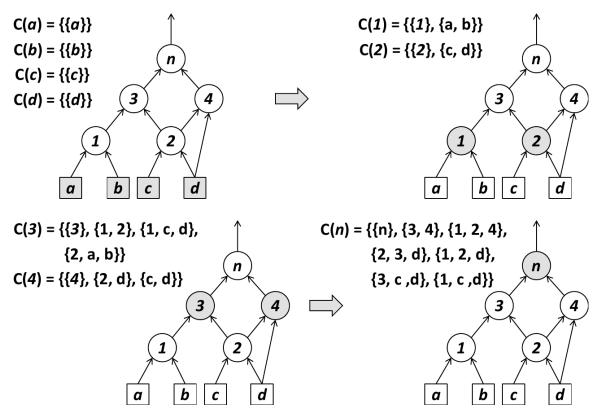

Another methodology handling subgraphs, called cuts, is used in the most AIG optimization techniques and they are also necessary for this work. Because cuts have been already published many times, the following text is a survey of [68, 66, 79, 101] with adaptation to the thesis purposes.

A cut C of a node n is a set of nodes of the graph, called leaves of the cut, such that each path from a *primary input* to n passes through at least one leaf. Node n is called the root of cut C. The cut *size* is the number of its leaves [68, 66]. See formal definition 6.

#### Definition 6. Cut

For a given AIG A = (V, E, X), a pair (v, L) consisting of a root  $v \in V$  and leafs  $L \subseteq V \setminus \{0\}$  is called a cut (see [79, 66, 68]), if

- 1. every path from v to a terminal visit at least one leaf  $l \in L$ ,

- 2. each leaf is contained in at least one path from v,

- 3. paths to the constant node are exempt from (1) and (2) constraints,

A set of all cuts of node v is denoted cuts(v). In other words,  $cuts(v) = \{L | L \subseteq V \{0\}$  so that (v, L) is a cut $\}$ .

A trivial cut, let us say a "seed" can be defined as follows, definition 7:

#### Definition 7. Trivial cut

In order to deduce a set of all possible cuts of node v, we can define a k-feasibility, definition 8:

#### Definition 8. k-Feasible cut

A cut is called k-feasible if  $|L| \leq k$ . A set of all k-feasible cuts is denote  $\operatorname{cuts}_k(v)$ . In other words  $\operatorname{cuts}_k(v) = \{L|(v,L) \text{ is a cut and } |L| \leq k\}.$

**Example 1.** Let  $C = (12, \{1, 4, 7, 9\})$  be a cut with a root 12 and leaves 1, 4, 7 and 9. As we can see, this cut is 4-feasible, i.e.  $\{1, 4, 7, 9\} \in cuts_4(12)$ .

All k-feasible cuts can be generated by a recursive algorithm. For cut enumeration purposes, an operation  $\otimes$  is defined, see definition 9:

#### Definition 9. Cut construction operation

Let  $A_1$  and  $A_2$  be two sets of cuts of a common root v and k a maximum number of leafs of new cut. Then  $A_1 \otimes A_2 \equiv \{a_1 \cup a_2 | a_1 \in A_1, a_2 \in A_2, |a_1 \cup a_2| \le k\}$ .

Now, it is possible to set a set of k-feasible cuts of node v:

#### Lemma 1. Recursive cut enumeration

$cuts_k(v) = cuts_k(v_{-1}) \otimes cuts_k(v_{-2})$ , where  $v \in V$  and  $v_{-1}, v_{-2}$  are direct children of node v, for  $\forall v = \{0..n\}$ .

Based on the previous definitions, it is possible to demonstrate an example of 3-feasible cuts enumeration in figure 3.2.

Figure 3.2: Example of 3-feasible cuts enumeration.

#### **KL-Cuts**

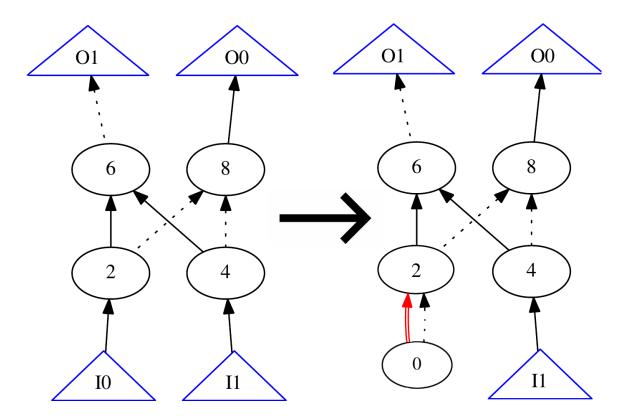

KL-cut can be defined as a subgraph  $G_{kl}$  of G, having  $inputs \leq k$  and also  $outputs \leq l$ . Inputs and outputs are represented by two sets of nodes  $(G_k, G_l)$ , where  $G_k$  is a set of inputs and  $G_l$  is a set of outputs. If a node v belongs to a path between  $n_k \in G_k$  and  $n_l \in G_l$  and  $v \notin G_k$ , then v is in  $G_{kl}$ . All nodes in  $G_l$  are contained in  $G_{kl}$  and  $G_{kl}$  doesn't contain any node of  $G_k$  [59].

Differences between K and KL-cuts are following. Based on the definition in the previous paragraph, k-cut is a sub-circuit of a circuit which has exactly k primary inputs and *one* primary output. KL-cut is a sub-circuit of circuit which has k primary inputs and l primary outputs. See figure 3.3 for examples of K-cut and KL-cut.

Figure 3.3: Example of k=3 cut is on the left and situation for k=3 in case of multi-output cut with two outputs is shown on the right.

#### Cut factorization

Enumeration of limited size cuts is a significant step in logic synthesis methods, such as technology mapping or rewriting. The cut enumeration algorithm isn't capable to enumerate all cuts beyond 7 inputs, because there are too many of them. Fortunately, researchers from University of Berkeley introduced *cut factorization* method [15], so that they can factor cuts of a network and use them to generate other cuts. With the factorization method, new terms had been presented (definitions 10 and 11):

#### Definition 10. DAG cut

DAG cut/Factor cut is a cut of a node v in an AIG, which has two or more outputs from the node v.

#### Definition 11. Tree cut

Tree cut is a cut of node v in an AIG, which has only one output of node v.

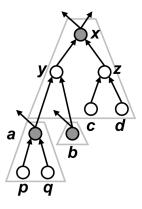

A reader can see an example of cut factorization on figure 3.4, that shows a decomposition of an AIG into factor trees. DAG/factor nodes are gray (see more than one output). Using the cut factorization, it is possible to reduce number of cuts significantly and thus

reduce time for enumeration. For more details and experiments, see literature [15].

Figure 3.4: An AIG subgraph illustrating cut factorization. Nodes p, q, b, c and d are PIs [15].

#### **NPN** Classification

Cuts are a good technique for subgraph selection in DAGs, the number of all functions growths exponentially size as the number of inputs increase. The number of all functions can be calculated as  $2^{2num}$ \_inputs. For example, if we are looking for all 4-input functions, the real number of all function is 65536. For 5-input cuts, the count of all combinations is 4294967296 [18].

In order to reduce the number of all combinations, NPN<sup>2</sup> classes were established. NPN classes allows to merge some circuits into equivalent one by permutation of inputs, negations or output negations.

- P-class: n-input functions equivalent under input permutations.

- NP-class: n-input functions equivalent under input permutations and negations.

- NPN-class: n-input functions equivalent under input permutations/negations and output negations.

The table 3.1 shows numbers of required functions merged into equivalent classes.

| Inputs | Functions  | P-classes | NPN-classes |

|--------|------------|-----------|-------------|

| 1      | 4          | 4         | 2           |

| 2      | 16         | 12        | 4           |

| 3      | 256        | 80        | 14          |

| 4      | 65536      | 3984      | 222         |

| 5      | 4294967296 | 37333248  | 616126      |

Table 3.1: NPN classes for numbers of inputs 1 - 5.

$<sup>^2</sup>$  NPN - Negation of inputs, Permutation of inputs, Negation of outputs.

#### 3.1.2 Structural hashing

The first optimization technique is not a technique at all, but rather a property. AIGs are usually implemented as a hash table in software. Hash table key of a node is made of two previous nodes. If any new node should have the same predecessors as an existing node, the keys will match and new node is merged with existing one. Thus, structural hashing detects isomorphic subgraphs in a AIG. It leads to the fact, that the two nodes can't be redundant in an examined AIG.

#### 3.1.3 Balancing

Reducing delay of a digital circuit is a significant topic in logic synthesis and therefore it has long history since early days of logic design.

Balancing [19, 66] is a technique widely known from graph theory and it is also applicable on AIGs. This technique is used for reducing depth of a network - reducing delay of a circuit, which is an important topic in logic synthesis.

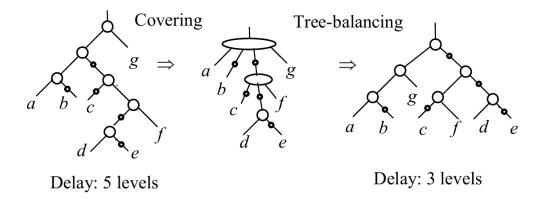

Balancing is an algebraic tree-height reduction, performed by application of Boolean rules such as commutativity, distributivity and associativity, for example: a(bc) = ab(c). Balancing operation has linear time complexity  $\Omega(n)$  and it is frequently used to minimize logic depth. Figure 3.5 shows an example of balancing technique.

Figure 3.5: An example of AIG balancing transformation [66].

#### 3.1.4 Refactoring

An optimization algorithm, mainly used for network area optimization, is refactoring. Refactoring uses a heuristic algorithm [67] to compute one large cut for each AIG node. Then, the refactoring attempts to replace cut of the current node by factored form. If there is an improvement, the modification is accepted [68].

#### 3.1.5 Resubstitution

A resubstitution is another optimization method, also based on enumeration of one large cut for each node. It tries to re-express a Boolean function of a node by reusing other nodes present in a network, known as divisors (see section 2.4.1). Similarly to refactoring, if a smaller network is obtained, the transformation is approved [67, 51].

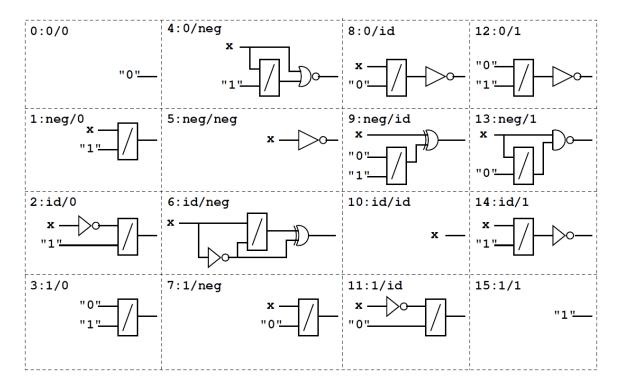

#### 3.1.6 Rewriting

Rewriting is another important optimization method for reduction the network size. It is fast greedy algorithm for optimization the AIGs by iteratively selecting AIG subgraphs - cuts (see section 3.1.1) rooted at a node and replacing them with smaller, functionally equivalent, pre-computed subgraphs. Original algorithm uses typically 4-feasible cuts, that are enumerated using the cut enumeration algorithm (see definition 9) [79]. For each cut of each node n, the Boolean function is computed and its NPN-class (see section 3.1.1) is recognized by hash-table lookup. Truth tables, stored as 16-bit strings, are used for fast handling of 4-input optimum functions. If we recall an idea of NPN classes, it is required to have only 222 variants of optimized subgraphs. It has been experimentally found that approximately 100 of 222 optimum circuits are appearing in the rewriting process and only 40 of them are meaningful, in terms of network improvement [68].

```

Rewriting( network AIG, hash table PrecomputedStructures, bool UseZeroCost )

for each node N in the AIG in the topological order {

for each 4-input cut C of node N computed using cut enumeration {

F = Boolean function of N in terms of the leaves of C

PossibleStructures = HashTableLookup( PrecomputedStructures, F );

// find the best logic structure for rewriting

BestS = NULL; BestGain = -1;

for each structure S in PossibleStructures {

NodesSaved = DereferenceNode( AIG, N );

NodesAdded = ReferenceNode( AIG, S );

Gain = NodesSaved - NodesAdded;

Dereference(AIG, S); Reference(AIG, N);

if ( Gain > 0 || (Gain = 0 && UseZeroCost) )

if ( BestS = NULL || BestGain < Gain )

BestS = S; BestGain = Gain;

if (BestS == NULL) continue;

// use the best logic structure to update the netlist

NodesSaved = DereferenceNode( AIG, N ):

NodesAdded = ReferenceNode( AIG, S ):

assert( BestGain = NodesSaved - NodesAdded );

}

}

}

```

Figure 3.6: Rewriting algorithm [68].

Figure 3.6 describes the AIG rewriting process, where the nodes are investigated in bottom-top topological order. Then, for each 4-feasible cut C of a node N, it obtains a boolean function F. Using hash-table lookup, it finds all possible structures. Subsequently, for each possible structure try: dereference old subgraph and the number of nodes, whose reference counts became 0, is returned. These nodes will be removed if the old subgraph is replaced. Then, a possible structure is added while counting the number of new nodes and the nodes whose reference count went from 0 to a positive value. These nodes will be added. The difference of the counters is the gain in the number of nodes if the replacement is done. The new node is de-referenced and the old node is referenced to return the AIG to its original state. While trying all possible structures, the maximum gain is remembered. The structure with maximum gain is then applied. If the improvement is zero and "zero-cost" is enabled, the possible structure is replaced [68].

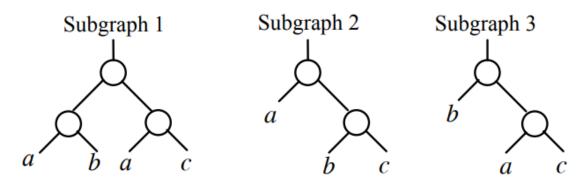

Figure 3.7: Different AIG structures for function F = abc [68].

Figure 3.8: An example of rewrite procedure [68].

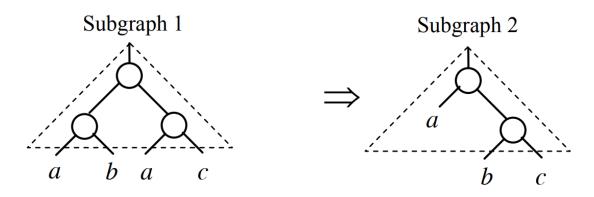

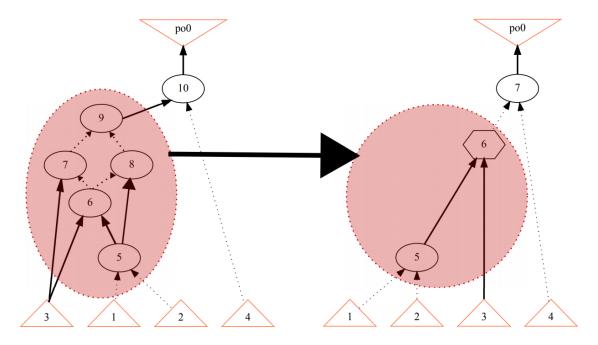

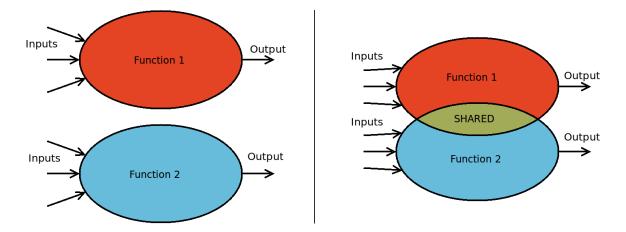

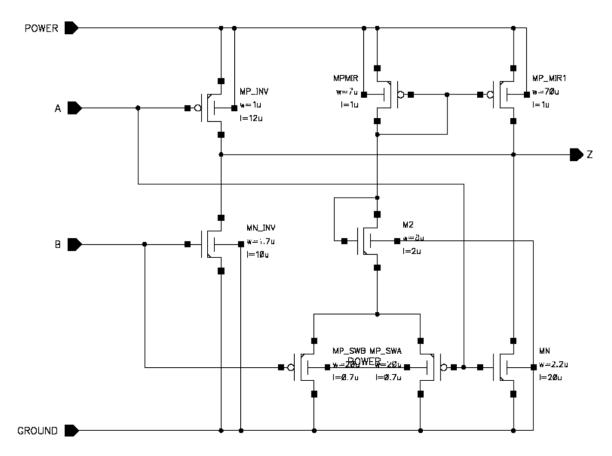

Figure 3.7 illustrates three possible structures of function F = abc. Figure 3.8 shows a replacement of subgraph 1 by subgraph 2, where it is possible to see one node reduction.

Rewriting algorithm leads to significant area improvements in logic synthesis and gave a lot of opportunities for further research.

#### Further work on AIG rewriting

The AIG rewriting has prepared a stable basis for local transformations of logic optimization. Rewriting is implemented in ABC tool [1] with opened sources, which allows source code modification by other researchers.

In 2007, authors of combinatorial AIG rewriting algorithm extended the algorithm for sequential circuits synthesis and introduced a new term: HAIG (History And-Inverter Graph) [12].

In 2011, Nan Li and Elena Dubrova proposed an extension of combinatorial rewriting. Researchers have tried to enable 5-input cuts in the original rewriting. However, as you can see in section 3.1.1, the number of functions, belonging to NPN equivalence classes, are 616162, that is still a high number. They experimentally checked which 5-input functions are appearing in all IWLS 2005 benchmarks [17] (2749 classes). After that, function (classes) with higher than twenty occurrences had been picked up (1185 classes). All these functions

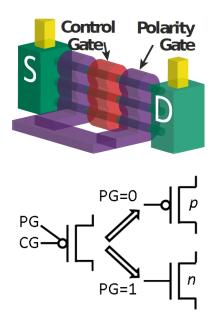

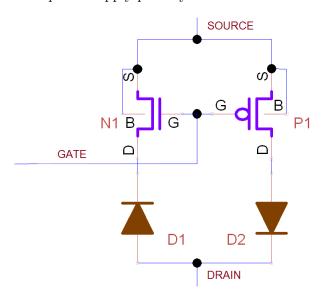

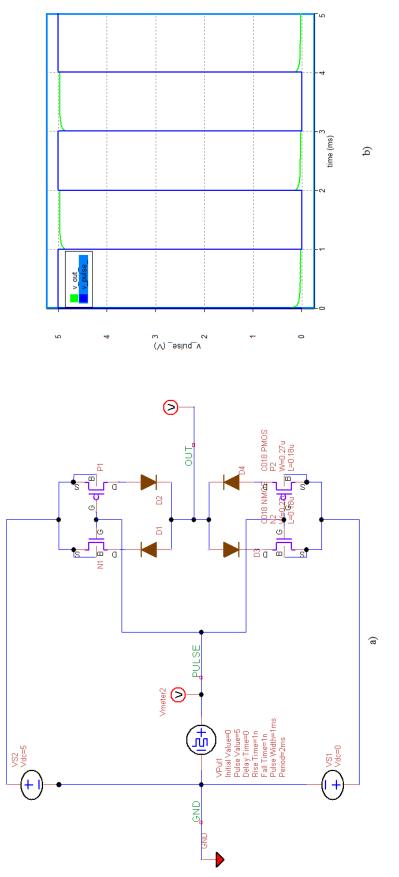

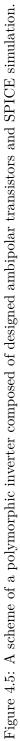

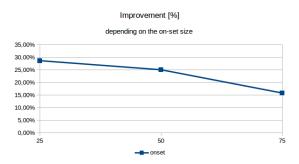

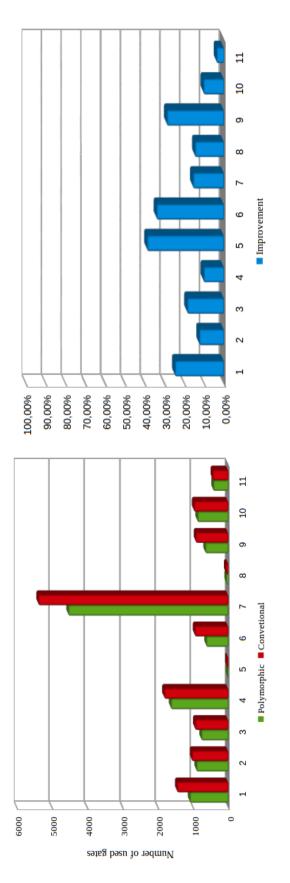

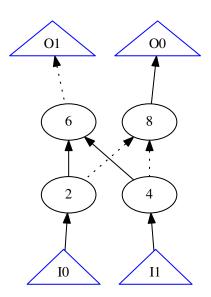

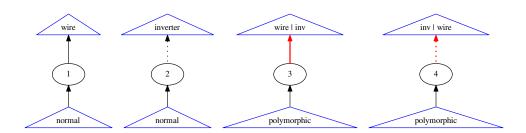

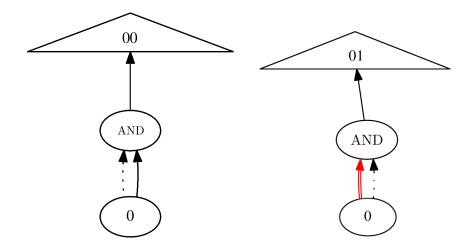

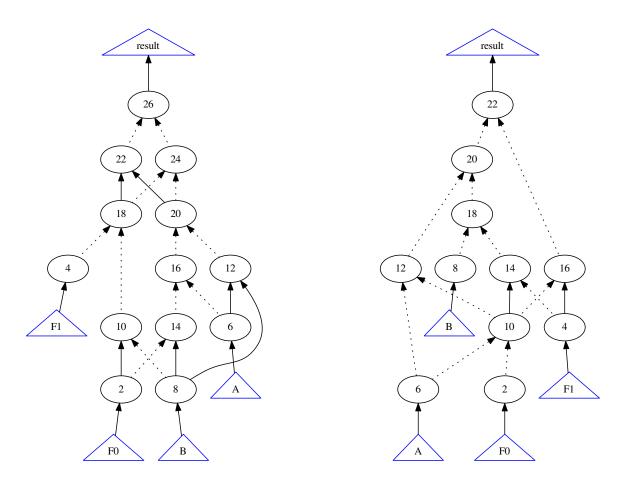

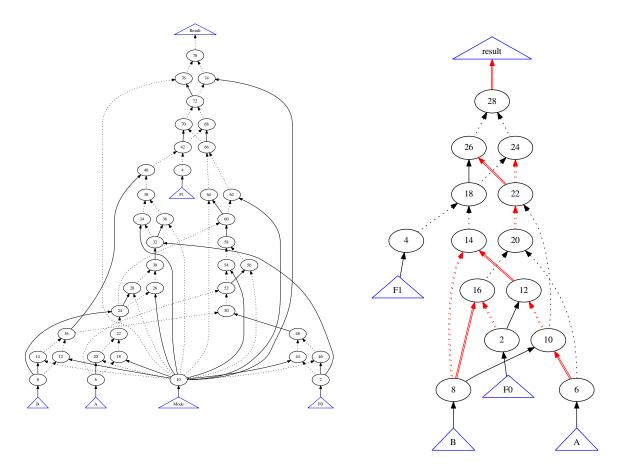

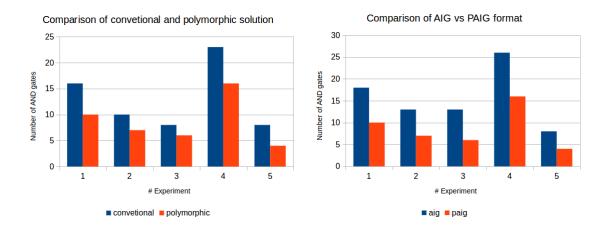

(classes) had been precomputed and applied for 5-input cut rewriting. Researches achieved about 5.57% further reduction of area of heavily optimized large circuits on average [55].