## **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF INFORMATION TECHNOLOGY

FAKULTA INFORMAČNÍCH TECHNOLOGIÍ

### **DEPARTMENT OF COMPUTER SYSTEMS**

ÚSTAV POČÍTAČOVÝCH SYSTÉMŮ

# NOVEL APPROACH TO POLYMORPHISM IN GATE-LEVEL DIGITAL CIRCUITS

NOVÝ PŘÍSTUP K POLYMORFISMU ČÍSLICOVÝCH OBVODŮ NA ÚROVNI HRADEL

### **EXTENDED ABSTRACT OF A PHD THESIS**

ROZŠÍŘENÝ ABSTRAKT DISERTAČNÍ PRÁCE

AUTHOR Ing. JAN NEVORAL

**AUTOR PRÁCE**

SUPERVISOR doc. Ing. RICHARD RŮŽIČKA, Ph.D., MBA

ŠKOLITEL

**BRNO 2019**

#### Abstract

Nearly twenty years ago, a non-conventional approach to implementation of multifunctional circuits called polymorphic electronics was proposed. The concept of polymorphic electronics allows to implement two or more functions in a single circuit, whereas the currently selected function depends on the state of the circuit operating environment. Key components of such circuits are polymorphic gates. Since the introduction of polymorphic electronics, several dozens of polymorphic gates have been published. However, a large number of them do not meet reasonable parameters. As a result, perspective of their utilisation for real applications becomes rather bleak. This dissertation introduces a new approach to the polymorphic electronics. It is based on gates whose behaviour depends on polarity of dedicated power supply rails. The goal of this thesis is to show that such approach allows to design gates with significantly better parameters. In order to systematically design proposed gates at the transistor level, an evolutionary method based on Cartesian genetic programming was proposed. That allowed to design several sets of efficient polymorphic gates employing conventional MOSFET and emerging double-gate ambipolar transistors. These gate sets were arranged into a library which is currently freely available for other researchers. Furthermore, a number of more complex circuits based on proposed gates were designed in this thesis. It is demonstrated at various levels of circuit design (gate, RTL, application) that the proposed gate-level polymorphism provides significant advantages compared to the first generation of polymorphic gates, but it can also be competitive or even better compared to the conventional CMOS solutions.

# Keywords

Polymorphic electronics, multifunctional gate, polymorphic gate, ambipolar transistor, MOSFET, digital circuit, PoLibSi.

### Reference

NEVORAL, Jan. Novel approach to polymorphism in gate-level digital circuits. Brno, 2019. Extended abstract of a PhD thesis. Brno University of Technology, Faculty of Information Technology. Supervisor doc. Ing. Richard Růžička, Ph.D., MBA

# Contents

| 1            | Intro | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2  |  |  |  |  |  |  |  |  |  |

|--------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|

|              | 1.1   | Polymorphic electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3  |  |  |  |  |  |  |  |  |  |

|              | 1.2   | Open problems of polymorphic electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4  |  |  |  |  |  |  |  |  |  |

|              | 1.3   | Research objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4  |  |  |  |  |  |  |  |  |  |

|              | 1.4   | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5  |  |  |  |  |  |  |  |  |  |

|              | 1.5   | Abstract outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6  |  |  |  |  |  |  |  |  |  |

|              |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |  |  |  |  |  |

| 2            | Surv  | vey of the state of the art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7  |  |  |  |  |  |  |  |  |  |

|              | 2.1   | Applications of polymorphic electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7  |  |  |  |  |  |  |  |  |  |

|              | 2.2   | Synthesis of polymorphic circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9  |  |  |  |  |  |  |  |  |  |

|              | 2.3   | Polymorphic gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10 |  |  |  |  |  |  |  |  |  |

|              |       | 2.3.1 Gates controlled by supply voltage level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11 |  |  |  |  |  |  |  |  |  |

|              |       | 2.3.2 Gates controlled by chip temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13 |  |  |  |  |  |  |  |  |  |

|              |       | 2.3.3 Gates controlled by dedicated control signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14 |  |  |  |  |  |  |  |  |  |

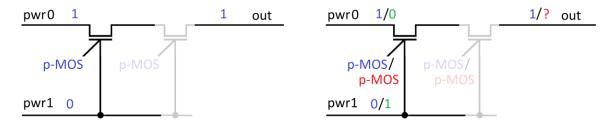

|              |       | 2.3.4 Gates controlled by supply voltage polarity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16 |  |  |  |  |  |  |  |  |  |

|              |       | 2.3.5 Non-conventional multifunctional gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20 |  |  |  |  |  |  |  |  |  |

|              |       | 2-010 1101 COLVOING MAINTAINCE SANCE TO THE TOTAL THE TOTAL SANCE TO T |    |  |  |  |  |  |  |  |  |  |

| 3            | Rese  | desearch summary 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |  |  |  |  |  |  |  |  |  |

|              | 3.1   | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22 |  |  |  |  |  |  |  |  |  |

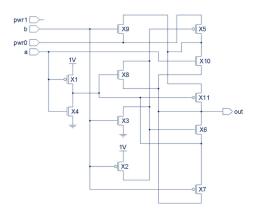

|              | 3.2   | Problem of a constant in the environment with changing power supply polarity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23 |  |  |  |  |  |  |  |  |  |

|              | 3.3   | Papers included in the thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25 |  |  |  |  |  |  |  |  |  |

|              |       | 3.3.1 Paper I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25 |  |  |  |  |  |  |  |  |  |

|              |       | 3.3.2 Paper II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27 |  |  |  |  |  |  |  |  |  |

|              |       | 3.3.3 Paper III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28 |  |  |  |  |  |  |  |  |  |

|              |       | 3.3.4 Paper IV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30 |  |  |  |  |  |  |  |  |  |

|              |       | 3.3.5 Paper V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32 |  |  |  |  |  |  |  |  |  |

|              |       | 3.3.6 Author's contributions to selected papers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33 |  |  |  |  |  |  |  |  |  |

|              | 3.4   | Following results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33 |  |  |  |  |  |  |  |  |  |

|              | 0.1   | 3.4.1 Power consumption of proposed gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33 |  |  |  |  |  |  |  |  |  |

|              |       | 3.4.2 Applications of proposed gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35 |  |  |  |  |  |  |  |  |  |

|              | 3.5   | List of other publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 38 |  |  |  |  |  |  |  |  |  |

|              | 3.6   | Research projects and grants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 38 |  |  |  |  |  |  |  |  |  |

|              | 5.0   | nesearch projects and grants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30 |  |  |  |  |  |  |  |  |  |

| 4            | Con   | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |  |  |  |  |  |  |  |  |  |

|              | 4.1   | Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39 |  |  |  |  |  |  |  |  |  |

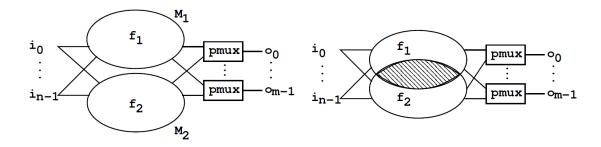

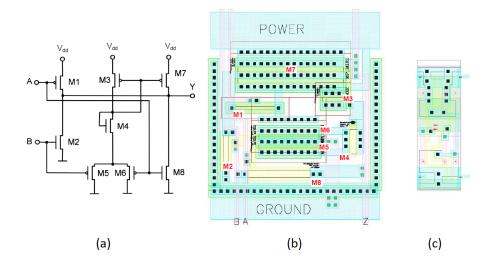

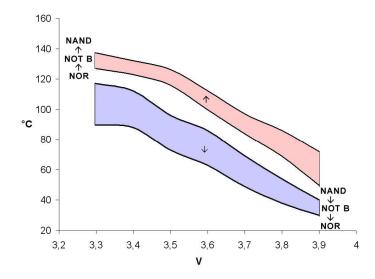

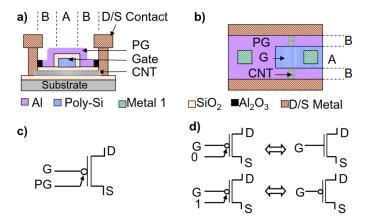

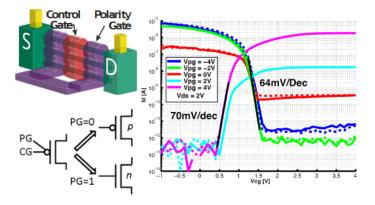

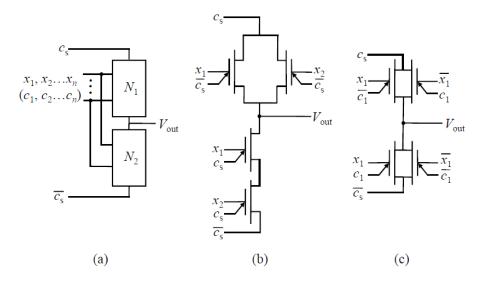

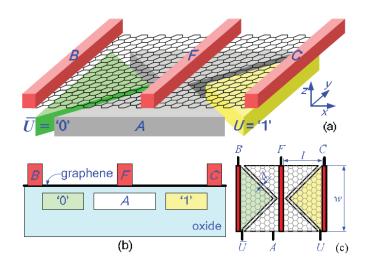

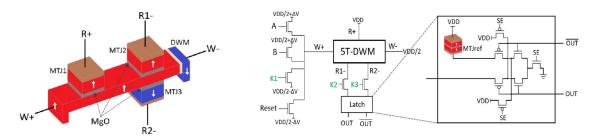

|              | 4.2   | Developed library available online                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40 |  |  |  |  |  |  |  |  |  |