# BRNO UNIVERSITY OF TECHNOLOGY VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

FACULTY OF INFORMATION TECHNOLOGY DEPARTMENT OF COMPUTER SYSTEMS

FAKULTA INFORMAČNÍCH TECHNOLOGIÍ ÚSTAV POČÍTAČOVÝCH SYSTÉMŮ

DATA LOADER FOR COMPLEX TESTING OF ON-BOARD SYSTEMS DATA LOADER PRO KOMPLEXNÍ TESTOVÁNÍ PALUBNÍCH SYSTÉMŮ

MASTER'S THESIS DIPLOMOVÁ PRÁCE

AUTHOR Bc. DAVID HRBEK AUTOR PRÁCE

ADVISOR doc. Ing. RICHARD RŮŽIČKA, Ph.D., MBA

VEDOUCÍ PRÁCE

## Vysoké učení technické v Brně - Fakulta informačních technologií

Ústav počítačových systémů

Akademický rok 2017/2018

# Zadání diplomové práce

Řešitel:

Hrbek David, Bc.

Obor:

Počítačové a vestavěné systémy

Téma:

Data loader pro komplexní testování palubních systémů

**Data Loader for Complex Testing of On-Board Systems**

Kategorie: Vestavěné systémy

#### Pokyny:

1. Prostudujte problematiku současných palubních systémů letadel, zaměřte se na standardy ARINC související s "data load", především ARINC 615A.

2. Seznamte se s jednotkou pro satelitní komunikaci Aspire 400 od firmy Honeywell. Analyzujte softwarové konfigurace jednotky Aspire 400 pro testování i letový mód. Seznamte se s nástroji pro přechod mezi softwarovými konfiguracemi jednotky Aspire 400.

3. Navrhněte pro jednotku Aspire 400 data loader, který umožní automatizované nahrávání všech

potřebných softwarových konfigurací.

4. Navržený data loader implementujte v souladu se standardem ARINC 615A.

5. Ověřte realizované řešení a demonstrujte funkčnost ve sledovaných aspektech.

#### Literatura:

Dle pokynů vedoucího.

Při obhajobě semestrální části projektu je požadováno:

Splnění bodů 1 a 2 zadání.

Podrobné závazné pokyny pro vypracování diplomové práce naleznete na adrese http://www.fit.vutbr.cz/info/szz/

Technická zpráva diplomové práce musí obsahovat formulaci cíle, charakteristiku současného stavu, teoretická a odborná východiska řešených problémů a specifikaci etap, které byly vyřešeny v rámci dřívějších projektů (30 až 40% celkového rozsahu technické zprávy).

Student odevzdá v jednom výtisku technickou zprávu a v elektronické podobě zdrojový text technické zprávy, úplnou programovou dokumentaci a zdrojové texty programů. Informace v elektronické podobě budou uloženy na standardním nepřepisovatelném paměťovém médiu (CD-R, DVD-R, apod.), které bude vloženo do písemné zprávy tak, aby nemohlo dojít k jeho ztrátě při běžné manipulaci.

Vedoucí:

Růžička Richard, doc. Ing., Ph.D., MBA, UPSY FIT VUT

Datum zadání:

1. listopadu 2017

Datum odevzdání: 23. května 2018

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

Fakulta informačních technologií Ústav počítačových systémů a sítí 612.66 Brno, Božetěchova 2

prof. Ing. Lukáš/Sekanina, Ph.D. vedoucí ústavu

# **ABSTRACT**

This master's thesis summarizes theory on how to perform data load onto on-board computers of aircrafts. Specifically, how automated data load of Honeywell's Aspire 400 satellite data unit is done. First part of the text describes requirements and possible ways of the data load process, including standards that are applicable to this topic in the aeronautical industry. The second part describes the implementation of the data load process on the aforementioned unit.

#### **KEYWORDS**

data load, Aspire 400 satellite data unit, ARINC standards

## **ABSTRAKT**

Tato diplomová práce shrnuje teorii ohledně nahrávání dat (data load) do palubních počítačů letadel, konkrétně do satelitní datové jednotky Aspire 400 od firmy Honeywell. První část textu popisuje požadavky kladené na proces nahrávání dat a možné způsoby jeho provedení. Jsou zde také představeny standardy týkající se tohoto tématu v leteckém průmyslu. Druhá část se pak zabývá samotnou implementací procesu nahrávání dat na zmíněné jednotce.

# KLÍČOVÁ SLOVA

nahrávání dat, satelitní datová jednotka Aspire 400, standardy ARINC

HRBEK, David. *Data Loader for Complex Testing of On-Board Systems*. Brno, 2018, 71 p. Master's Thesis. Brno University of Technology, Faculty of Information Technology, Department of Computer Systems. Advised by doc. Ing. Richard Růžička, Ph.D., MBA

# **DECLARATION**

I declare that I have written the Master's Thesis titled "Data Loader for Complex Testing of On-Board Systems" independently, under the guidance of the advisor and using exclusively the technical references and other sources of information cited in the thesis and listed in the comprehensive bibliography at the end of the thesis.

As the author I furthermore declare that, with respect to the creation of this Master's Thesis, I have not infringed any copyright or violated anyone's personal and/or ownership rights. In this context, I am fully aware of the consequences of breaking Regulation  $\S 11$  of the Copyright Act No. 121/2000 Coll. of the Czech Republic, as amended, and of any breach of rights related to intellectual property or introduced within amendments to relevant Acts such as the Intellectual Property Act or the Criminal Code, Act No. 40/2009 Coll., Section 2, Head VI, Part 4.

| Brno | <br>               |

|------|--------------------|

|      | author's signature |

| ACKNOWLEDGEN                                                                                                                                                                         | 1ENT                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| I would like to thank my supervisor, doc. Ing. Richard I would also like to thank my supervisor at Honeywell the matter, and the company itself for allowing me to u on this thesis. | I, Bc. Petr Kartous, for his insights on |

| Brno                                                                                                                                                                                 | author's signature                       |

|                                                                                                                                                                                      |                                          |

# CONTENTS

| 1 | Intr | roduction                | 9    |

|---|------|--------------------------|------|

| 2 | Dat  | a Load Definition        | 10   |

| 3 | AR   | INC standards            | 11   |

|   | 3.1  | ARINC 429                | 12   |

|   | 3.2  | ARINC 600                | 14   |

|   | 3.3  | ARINC 615                | 15   |

|   | 3.4  | ARINC 615A               | 16   |

|   | 3.5  | ARINC 664                | 18   |

|   | 3.6  | ARINC 665                | 19   |

|   | 3.7  | ARINC 781                | 20   |

| 4 | Asp  | pire 400                 | 22   |

|   | 4.1  | SDU structure            | 22   |

|   |      | 4.1.1 MPC                | 23   |

|   |      | 4.1.2 DABC               | 25   |

|   |      | 4.1.3 SCM                | 27   |

|   | 4.2  | MPC Software Parts       | 28   |

|   |      | 4.2.1 FPGA Configuration | 28   |

|   |      | 4.2.2 RCW                | 28   |

|   |      | 4.2.3 Miniboot           | 28   |

|   |      | 4.2.4 U-Boot             | 28   |

|   |      | 4.2.5 HBIT               | 29   |

|   |      | 4.2.6 Flight Code        | 30   |

|   | 4.3  | DABC Software Parts      | 30   |

|   |      | 4.3.1 FPGA Configuration | 31   |

|   |      | 4.3.2 Loader Program     | 31   |

|   |      | 4.3.3 EBOOT              | 33   |

|   |      | 4.3.4 IBIT               | 33   |

|   |      | 4.3.5 SwiftBB            | 33   |

|   | 4.4  | ATE                      | 33   |

| 5 | Dat  | a Load Scenarios         | 35   |

| J | 5.1  | MPC Data Load Scenarios  | 37   |

|   | 5.2  | DABC Data Load Scenarios | 38   |

| c | т    |                          | 40   |

| 6 |      | ding low level software  | 40   |

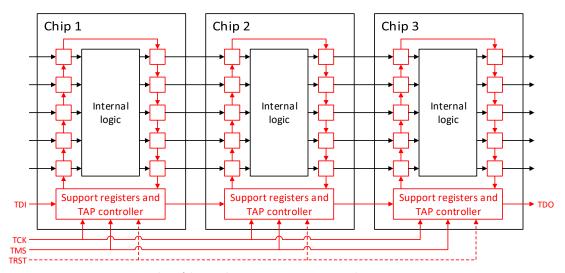

|   | 6.1  | Boundary Scan            | 40   |

|   | 6.2  | In-system Programming    | 43   |

|   | D .5 | riasinno MPC.            | 41.3 |

|               | 6.4           | Flashing DABC                    | 44        |  |  |

|---------------|---------------|----------------------------------|-----------|--|--|

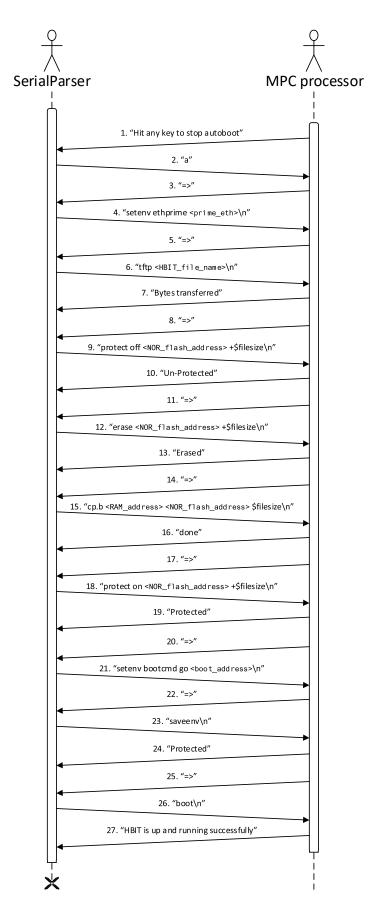

| 7             | $\mathbf{MP}$ | C Data Load Using U-Boot         | 45        |  |  |

|               | 7.1           | Requirements                     | 45        |  |  |

|               | 7.2           | Design                           | 46        |  |  |

|               |               | 7.2.1 Settings File              | 47        |  |  |

|               |               | 7.2.2 Patterns File              | 47        |  |  |

|               |               | 7.2.3 Call Options               | 48        |  |  |

|               |               | 7.2.4 Communication Processing   | 48        |  |  |

|               |               | 7.2.5 User Control               | 49        |  |  |

|               |               | 7.2.6 Logging and Error Handling | 49        |  |  |

|               | 7.3           | Implementation                   | 49        |  |  |

|               | 7.4           | Verification and Validation      | 51        |  |  |

| 8             | DA            | BC Data Load                     | <b>54</b> |  |  |

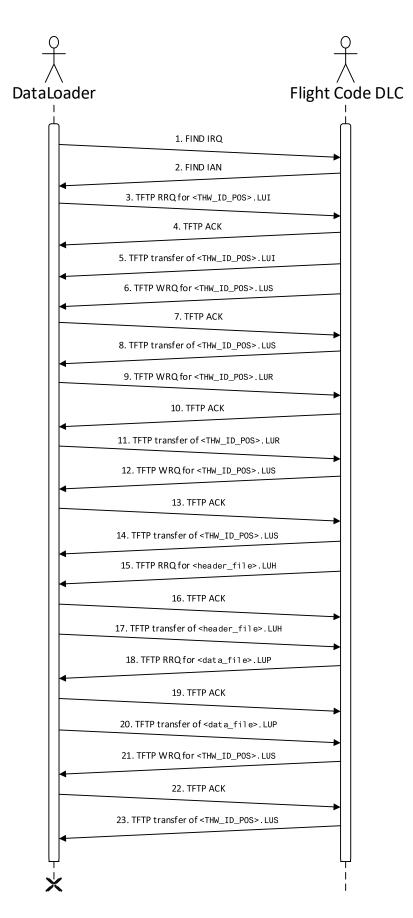

| 9             | AR            | INC 615A Compliant Data Load     | 56        |  |  |

| Ü             | 9.1           | Requirements                     | 56        |  |  |

|               | 9.2           | Design                           | 57        |  |  |

|               | 5.2           | 9.2.1 SDU Side                   | 57        |  |  |

|               |               | 9.2.2 FIND Protocol              | 58        |  |  |

|               |               | 9.2.3 TFTP                       | 59        |  |  |

|               |               | 9.2.4 Console Interface          | 61        |  |  |

|               |               | 9.2.5 GUI                        | 61        |  |  |

|               |               | 9.2.6 TestStand Interface        | 62        |  |  |

|               | 9.3           | Implementation                   | 63        |  |  |

|               | 9.4           | Verification and Validation      | 63        |  |  |

|               | 0.1           |                                  |           |  |  |

| 10            | Con           | clusions                         | 64        |  |  |

| Bi            | Bibliography  |                                  |           |  |  |

| $\mathbf{Li}$ | st of         | abbreviations                    | 69        |  |  |

# LIST OF FIGURES

| 3.1 | ARINC 600 connector on LRU backplane                                        | 14 |

|-----|-----------------------------------------------------------------------------|----|

| 4.1 | Aspire 400 SDU loadable components and their interconnections $\dots \dots$ | 23 |

| 4.2 | MPC processor block diagram                                                 | 24 |

| 4.3 | DABC processor block diagram                                                | 27 |

| 4.4 | DABC application selection                                                  | 32 |

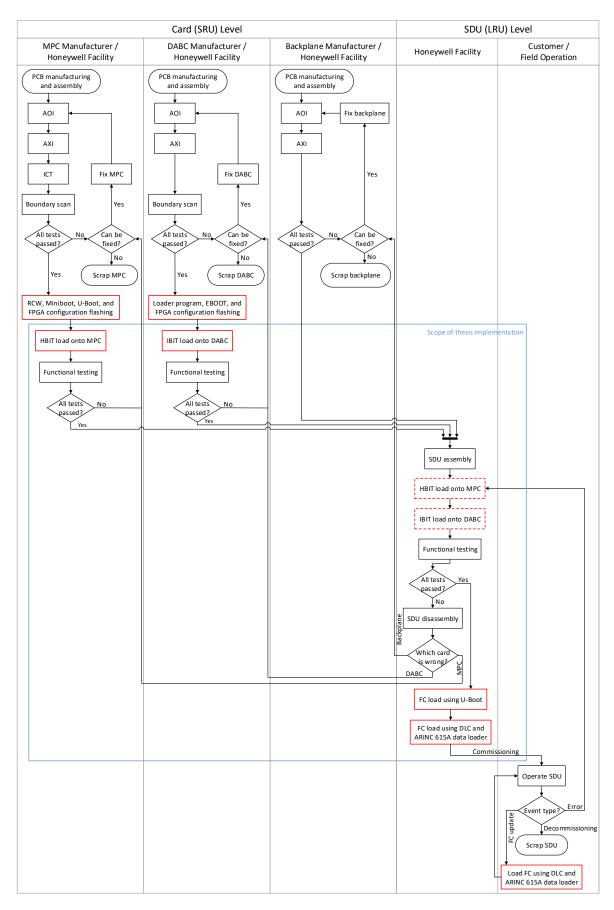

| 5.1 | Aspire 400 SDU lifecycle with data loads highlighted                        | 36 |

| 6.1 | Principle of boundary scan testing and in-system programming                | 41 |

| 7.1 | Sequence diagram of HBIT data load onto MPC processor                       | 52 |

| 9.1 | Sequence diagram of data load process initiated by DataLoader               | 60 |

# 1 INTRODUCTION

This master's thesis Data Loader for Complex Testing of On-Board Systems was implemented in cooperation with Honeywell company. The goal was to come up with a way of automated and reliable data load of Aspire 400 satellite data unit (SDU). Aspire 400 is an aircraft on-board unit, currently under development at Honeywell. The unit has to use various software configurations during its life cycle, therefore there were multiple data load scenarios that needed to be considered.

In this document, the data load process in general is described (see chapter 2), including some of the important applicable standards used in aeronautical industry (see chapter 3). After this theoretical part, the Aspire 400 product is described, with emphasis on the key components, their software parts, and the equipment used in the production process (see chapter 4). Another chapter is devoted to possible data load scenarios (see chapter 5). The description of the data load process and its implementation is split into several subprocesses, starting with data load of the low level software parts (see chapter 6), over the first time data load of the target software (see chapter 7 and chapter 8), to the final ARINC 615A compliant data load (see chapter 9). In the end, the results of this thesis are summarized, together with ideas for possible improvements (see chapter 10).

The main scope of the thesis were the data load scenarios used in production on the unit level. See Figure 5.1 in chapter 5 for clarification. Implementation of these scenarios is described in chapter 7 and chapter 9.

Due to the commercial nature of the Aspire 400 project, this document is kept at a higher level of abstraction where possible. Of course, details important to the data load problematics are described as much as possible with compliance to Honeywell's policy of publishing information. Nevertheless, some of the information within this document can be regarded as Honeywell's intellectual property and should be treated as such. Any usage of information about the Aspire 400 project should be consulted with Honeywell.

# 2 DATA LOAD DEFINITION

Data load is a process of writing specific software onto some device, called the target hardware. The software is usually low level, e.g. some kind of firmware or lightweight operating system. In the context of this document, the target hardware is an aeronautical equipment, but generally, it can be any piece of hardware that needs some software for operation.

Data load is performed using a data loader. Data loader can be some special hardware, but it can also be an ordinary PC. The only requirements are the support of the required interfaces, e.g. Ethernet, and software which is able to communicate with the target hardware.

Data loader can communicate with the target hardware directly, i.e. be connected straight to it, or it can be connected to a bus to which multiple devices, including the target hardware, are connected. In the latter case, data loader also needs to be able to address the correct device or devices on the bus.

The goal of the data load process is to write the desired data into non-volatile memory of the target hardware on appropriate addresses, so that the target hardware can boot up and operate using the loaded software. The non-volatile memory is nowadays usually electrically erasable programmable read-only memory (EEPROM) or flash memory.

It is data loader's responsibility to ensure the data load process is carried out properly, i.e. the data is written onto the target hardware correctly and the target hardware operates as expected. Therefore the data loader has to support at least error checking and should preferably support also error handling. If the data load process is unsuccessful, the data loader needs to clearly report this and should provide more information about the problem to its operator. The data loader can also try to revert the target hardware's configuration to the point it was in before starting the data load process.

The term data load is sometimes used not only for writing, or uploading, data onto a device. It can also be used to describe the process of getting, or downloading, data from the device. In the latter context, data loader can be used to get information about the device it is connected to. For example information about the purpose, type, configuration of the device, etc. can be obtained.

This is a general description of the data load process. It may seem to be quite vague, but there is no precise definition. However, there are standards with more specific requirements for the target hardware and the data loader. These are described in the next chapter.

# 3 ARINC STANDARDS

Aeronautical Radio, Incorporated (ARINC) is a company which was founded in 1929 by four starting United States airline companies. The goal of the company was to serve the communication needs of the transportation industry (see [1], page ii). Till 2007, ARINC was owned by shareholders, most of whom were airline companies, both U.S. and others. In July 2007, ARINC was bought from its shareholders by a private equity company called The Carlyle Group (see [2]) and in 2013 The Carlyle Group sold it to Rockwell Collins Inc. Since Rockwell Collins does business in avionics, it sold ARINC's Industry Standards Organization subsidiary to avoid any conflict of interest. It was bought by SAE International (see [3]). SAE originally stood for Society of Automotive Engineers, but nowadays it is a global association of engineers and technical experts in the aerospace, automotive and commercial-vehicle industries. One of their goals is voluntary consensus standards development (see [4]).

Therefore, the ARINC standards are currently issued by SAE ITC (ITC stands for Industry Technologies Consortia), more precisely by ARINC Industry Activities, an SAE ITC program (see [5], page ii). This program organizes aviation industry committees, one of them being the Airlines Electronic Engineering Committee (AEEC). AEEC is an international body of airline technical professionals that leads the development of technical standards for airborne electronic equipment, including avionics and in-flight entertainment equipment-used in commercial, military, and business aviation. The AEEC establishes consensus-based, voluntary form, fit, function, and interface standards that are published and which are known as ARINC standards (cited from [1], page ii). AEEC is the body that prepared the standards which are important for this thesis.

There are three classes of ARINC standards (cited from [1], page ii):

- ARINC Characteristics, which define the form, fit, function, and interfaces of avionics and other airline electronic equipment. ARINC Characteristics indicate to prospective manufacturers of airline electronic equipment the considered and coordinated opinion of the airline technical community concerning the requisites of new equipment including standardized physical and electrical characteristics to foster interchangeability and competition.

- ARINC Specifications, which are principally used to define either the physical packaging or mounting of avionics equipment, data communication standards, or a highlevel computer language.

- ARINC Reports, which provide guidelines or general information found by the airlines to be good practices, often related to avionics maintenance and support.

Below, mostly standards that are related to data load are briefly described. The class of each of the standards is specified and there is also a link to the bibliography, where information about the original documents can be found. In section 3.1, ARINC 429 is described. In section 3.3, ARINC 615 is described. In section 3.4, ARINC 615A is described. And in section 3.6, ARINC 665 is described.

There are other ARINC standards applicable to the data load process. The reason these are not described in greater detail here is that they are very outdated. For example ARINC report 603 (see [6]) sets expectations for data loader of airborne computers. However, this standard was released in 1985 and expects the data loader to transfer data from a tape cartridge.

Two exceptions can be found in the listed standards, namely ARINC 600, described in section 3.2, and ARINC 781, described in section 3.7. These standards are not data load related, but they are important for this thesis. ARINC 600 is important because it contains specifications and requirements put onto units, such as Aspire 400, in order for them to be compatible with standard airplane racks. And ARINC 781 sets characteristics of aviation satellite communication systems operating in L-band. Aspire 400 is such a system and that is the reason why the standard is described in this document as well.

# 3.1 ARINC 429

ARINC 429 is a four part ARINC specification (see [7], [8], [9], and [10]) subtitled *Digital Information Transfer System* (DITS), or *Mark 33 Digital Information Transfer System*. It defines a data bus widely used in avionics.

The standard describes physical and electrical interfaces of the bus, and also a protocol supporting local area network (LAN) within the aircraft. The term bus may be considered to be misleading in case of ARINC 429, since bus usually supports multidirectional transfers of data, while ARINC 429 supports only one way transfers from one source to up to 20 recipients. If the connected device needs both to transmit and receive, it has to do so on separate lines. Each line constitutes of one twisted and shielded pair of wires.

Bits are being transmitted using the bipolar return-to-zero modulation. This means clocking is part of the transmission. When transmitted, logical one has voltage of  $10 \pm 1 \,\mathrm{V}$ , logical zero has voltage of  $-10 \pm 1 \,\mathrm{V}$ . The bus supports two speeds of data transfer. High speed is 100 kbps a low speed is in range of 12 to 14.5 kbps. Data are transfered in 32 bit words. Words are separated on the bus by putting a gap of at least four bit periods between them. New word starts with the first bit transmitted after this gap. Most messages used on the bus consist of only one word, but packets of up to 512 words are allowed.

Each 32 bit word has to have 1 parity bit (bit 32, the most significant one) and an 8 bit label, which is stored in the 8 least significant bits (bits 8 to 1). The word is transmitted from the least to the most significant bit, i.e. label first, parity bit last. The parity bit allows simple error check at the receiver.

There are other bits that usually have set function within a word. Bits 10 and 9 can represent the so called source / destination identifier, which is used when the word needs to be addressed to a specific device. Bits 31 and 30, and in some cases also bit 29, represent sign / status matrix, which is used to report the hardware status of the device, but it can also be used to represent a predefined sign, e.g. plus / minus, north / south, east / west,

right / left, etc. More detailed information about the word formats can be found in [7], attachment 6 on pages 115 to 124.

The label is encoded as a 3 digit octal number, and its bits are actually flipped significance-wise, so the 2 least significant bits of the word form the most significant digit of the label, the next 3 least significant bits of the word form label's second digit, and the next 3 least significant bits of the word form label's third digit. This representation allows label to be in range of 0 to 377.

The label identifies the data type of the word, i.e. whether it is binary encoded, binary coded decimal encoded, or represents discrete values, and it also identifies what kind of information the data represent. For example, label with octal code 015 represents information about wind speed in binary coded decimal.

Since the amount of equipment that needs to communicate data within an aircraft increased a lot compared to the time the standard was first released, some labels are used in different contexts. To determine the context, the transmitting device is identified by the equipment ID. Equipment ID is encoded within a word as 3 hexadecimal digits, i.e. on 12 bits. The combination of label and equipment ID should always identify a unique type of message. The full list of these types can be found in [7], attachment 1 on pages 21 to 54.

Description of the binary encoded decimal labels and equipment IDs can be found in [7], attachment 2A on pages 55 to 60. The description states value ranges and resolution of the data, how many significant bits there are, in what units is the encoded number, etc. The same description for the binary encoded data can be found in [7], attachment 2B on pages 61 to 81. Definition of the words representing discrete values can be found in [8] (the whole document).

The data carried by a word can represent either numeric value, alphanumeric data encoded using ISO alphabet number 5, or graphic data. The last one is used to transfer data which are rendered on a display, e.g. a map in an aircraft.

ARINC 429 standard also defines techniques for file data transfer. File data can be transfered using either character oriented protocol, or bit oriented protocol, which is also called Williamsburg protocol. Two versions of bit oriented protocol are used.

Version 1 is described in [9], section 2.5 on pages 5 to 24. The description explains the concept of link data units (LDUs), which is used to split the data file into pieces that are sent using the data words, and then reassembled again. By definition, 3 to 255 words make up 1 LDU, and the size of the transmitted file should not exceed 255 LDUs. The protocol also contains details about system address labels, word timing, types of words used to manage the data transfer, e.g. request to send, start of transmission, end of transmission, etc.

Version 2 is not used anymore. It has been superseded by version 3, which is derived from version 1. Version 3 is IEEE 802 compliant MAC protocol using ISO/OSI data link layer. Details about architecture of this version can be found in [9], chapter 3 on pages 26 to 51.

# 3.2 ARINC 600

ARINC 600 is an ARINC specification called Air Transport Avionics Equipment Interfaces (see [11]). It defines mechanical, electrical, and environmental interfaces between the so called line replaceable units (LRUs) and the racks or cabinets in which they are installed.

LRU is a term used in avionics for a piece of modular on-board equipment, which, in case of its failure, can be quickly replaced. The malfunctioning module is simply replaced with a working one, and the service time, during which the aircraft has to be grounded, is reduced. This is beneficial, since it is very expensive for the aircraft's operator to

have it grounded. The malfunctioning unit can be then inspected and eventually repaired someplace else, e.g. its manufacturer's facility, and time is not so critical anymore.

Besides the definition of aforementioned interfaces, ARINC 600 also gives guidance for the design process and acceptance process of these interfaces. And interfaces between the racks or cabinets and the aircraft itself are covered in the same way, including control and regulation of power applied to on-board equipment. Interchangeability of LRUs and racks made by different suppliers is also discussed. Following ARINC 600 guidelines provides (taken from [11], page 3):

- a system of modularized equipment

- a system of modularized installation in racks and / or cabinets

- a family of low or zero insertion force electrical connectors to provide the electrical interface between the equipment and the aircraft wiring

- a system of effective environmental control of the equipment

The standard defines a so called modular concept unit (MCU), which is the basic unit for the packaging and installation concept of LRUs. MCU defines a fixed height, length, and width. All LRUs following ARINC 600 specification should have this height and length, and their width should be a multiple of width defined by MCU, i.e. the smallest LRU should have width of 1 MCU and bigger ones can have width of 2 MCUs, 3 MCUs, etc. Maximum weight of LRUs is defined as well.

Furthermore, ARINC 600 sets forth parameters for

Fig. 3.1: ARINC 600 connector on LRU backplane

maximum LRU thermal dissipation, cooling of on-board equipment within the racks, and requirements for attachment of LRUs to these racks, i.e. ways of physical mounting, forces the attachment has to withstand (vibration, shock, acceleration), etc.

However, the most important thing from ARINC 600 for the topic of this thesis is the definition of LRU's connector properties. It also covers the largest part of the ARINC 600 document itself ([11], attachments 17 to 21 and appendices 3 to 5). In these parts, the types of connectors that make up the whole ARINC 600 LRU connector are described, for example properties of pins for discrete signals, connectors for Ethernet, etc. An example of ARINC 600 connector can be found in Figure 3.1.

# 3.3 ARINC 615

ARINC 615 is an ARINC report called Airborne Computer High Speed Data Loader (see [12]). The last release of this standard was made in 2002. Today, it is quite outdated and it is described here mostly for legacy reasons and the description is not very detailed. Nevertheless, some devices still try to be compliant with this standard. Some parts of the standard are very similar to ARINC 615A standard, which is described in the next subsection. Since ARINC 615A standard is more important for this thesis, the similar parts are described there.

The standard sets guidelines for development of two types of data loaders. Portable data loader (PDL), and airborne data loader (ADL). Physical requirements for these devices are defined in the standard, same way they are defined for these devices in ARINC 615A.

The data loader is using ARINC 429 interface and should have at least two outputs and four inputs. It should be able to operate at both high speed (100 kbps) and low speed (12.5 to 14 kbps). The on-board computers should address it in the sent words using label with octal code 226 for high speed and label with octal code 300 for low speed.

The media for storing the loadable data are 3.5 inch floppy discs. The exact properties and format of a disc are described in [12], sections 3.2.1 and 3.2.2 on pages 7 and 8.

The standard describes two configurations files for the data loader. First is called *CONFIG.LDR*, and second is called *EXCONFIG.LDR*. At least one of them has to be present on the disc, and if there are both, *CONFIG.LDR* is processed first. The configuration file contains the physical parameters used for the communication with the target device, settings for the initial action taken after the initialization of the bus, total number of data discs required for the data load, sequence number of the current disc, etc. The full description of both types of configuration files can be found in [12], section 3.2.3.1 on pages 8 to 11, and section 3.2.3.2 on pages 11 and 12, respectively. If some of the required configurations are not set properly, default values are used.

File transfers are compliant with the file data transfer defined in ARINC 429. They use the so called command / response protocol. Three types of words are used in this protocol. Initial words, which are used to start and maintain the communication, intermediate words, which carry the actual file data, and final words, which contain checksum used for an error check and close the transmission. The whole scheme of the protocol is described in detail in [12], section 3.5 on pages 21 to 29.

# 3.4 ARINC 615A

ARINC 615A is an ARINC report called Software Data Loader Using Ethernet Interface (see [1]). It describes a data load protocol implemented using Trivial File Transfer Protocol (TFTP) and Ethernet interface for the physical connection. It is the most important standard regarding this thesis.

ARINC 615A sets expectations for and gives guidance on development of software data loading equipment. As already mentioned, primary goal of data load is to upload software onto the target hardware. Secondary goal can be to download information from the target hardware.

Even though the standard is focusing on data load over Ethernet, other avionics buses using elements of Ethernet protocol are also mentioned as possible physical connection for implementation of ARINC 615A data load protocol. Namely ARINC 615A over AFDX (see section 3.5) and ARINC 615A over CAN bus are mentioned.

The standard defines three categories of data load functionality:

- Portable Data Loader (PDL), which is a mobile device that can be used to perform data load on the ground or brought on-board of an aircraft to perform data load

- Airborne Data Loader (ADL), which is a device installed on an aircraft

- Data Load Function (DLF), which is a software performing the data load itself

The standard describes physical requirements for PDL and ADL, e.g. their size, weight, controls and indicators, power supply and circuitry, non-operating and operating temperature spans, etc.

Some recommendations regarding the removable transport media for the loadable software are also made. The media include for example USB sticks, CDs and DVDs, and legacy carriers like 3.5 inch floppy disks.

The most important part of the standard is the definition of the load protocol. It defines functions that are necessary to be implemented both on data loader side and the target hardware side for them to be ARINC 615A compliant.

The load protocol defines means to (cited from [1], page 22):

- upload ARINC 665 software parts (see section 3.6) to target hardware

- download data from target hardware

- get configuration information from target hardware

- interrupt at any time any of the three previous operations (interruption request can be made by the operator or by the target hardware)

- obtain subscriber information, such as MAC address, IP address, and target hardware identifier

To the last point, the subscriber information can be obtained using the Find Identification of Network Devices (FIND) protocol. FIND protocol allows its initiator (operator using the data loader) to identify all available FIND hosts (ARINC 615A compliant target hardware) on the network. The operator can then select the desired target hardware device or devices from a list.

The implementation of the FIND protocol is done using UDP datagrams on port 1001. The initiator of the operation broadcasts or multicasts a request for a response from all available FIND hosts on the network. Then it registers all valid responses that come within 3 seconds.

FIND hosts respond with a unicast message to the data loader. Information about host's MAC address and IP address are part of the UDP/IP datagram and other information about the host are part of the UDP payload. FIND protocol does not implement any error handling. If the request or the response are not valid, they are ignored.

Two types of FIND packets are defined. Information request (IRQ) and information answer (IAN). Each has a two byte header defining whether it is an IRQ packet (value 1) or IAN packet (value 2) and a variable length data. IRQ carries only one byte ASCII string terminator (value 0x00) and one byte packet terminator (value 0x10).

IAN carries information identifying the host. It contains five strings separated by the one byte ASCII string terminator. These strings are:

- 1. Target Hardware Identifier

- 2. Target Hardware Type Name

- 3. Target Hardware Position

- 4. Literal Name

- 5. Manufacturer Code

All the other operations defined by ARINC 615A, excluding FIND, are implemented using TFTP protocol, i.e. they are based on downloading from or uploading files to the TFTP server, which is part of the data loader. There are two types of files that are exchanged between the data loader and the target hardware. First being protocol files that are generated during the load process, and second being the files with the loaded software itself. While standard TFTP port is 69, TFTP services for ARINC 615A are expected to run on port 59.

There are three types of operations defined in the standard, which are implemented using TFTP:

- Information Operation, during which the data loader acquires information about the configuration of the target hardware

- Uploading Operation, during which the data loader uploads files to the target hardware

- Downloading Operation, during which the data loader downloads file from the target hardware

According to the standard, data loader has to implement all of the above operations, plus the FIND operation defined earlier, whereas target hardware does not necessarily

need to implement the download operation. Furthermore, the operations cannot run in parallel, and active operation can be aborted upon a request from the operator.

TFTP options may be implemented to gain higher efficiency of the file transfer. In such case, the negotiation of these options has to be supported as well, though. If one side does not support any of the options, standard settings have to be used for this option or these options. Transfer should never fail due to non-implemented option.

Standard TFTP protocol is extended for the purpose of the load protocol. Wait and abort messages are defined by the load protocol. They are implemented using the TFTP error message. This message is part of an error packet and contains an error code number, and an ASCII error message. Defined error codes are integers from 0 to 8. Error code 0 definition is *Not defined*, see error message. Load protocol uses this error code and utilizes its error message to define its own string encoded messages.

Wait message contains error string WAIT:x, where x is the wait time in seconds. The maximum wait time is 65 535 seconds. This message can be generated in response to a TFTP transfer request by either the data loader or the target hardware. The device receiving this message should abort the TFTP transfer and initiate it again after the specified delay.

Abort message contains error string *ABORT:xxxx*, where *xxxx* is string of four hexadecimal digits containing a status code. The status code can for example mean that the operation was aborted by the data loader, or by the operator.

Any target hardware instance in an aircraft is defined by an identifier called *THW\_ID\_POS*. *THW\_ID* (target hardware identifier) is defined in ARINC 665 standard and *POS* (target hardware position) is represented by 0 to 8 alphanumeric characters. Both these strings are part of the IAN packet payload received upon a FIND request.

The THW\_ID\_POS identifier is used as a name for the generated protocol files, using different suffixes. The full list of the protocol files can be found in the original ARINC 615A document (see [1], table 6.4-1 on page 66). These files contain all the protocol overhead information like the protocol version supported by the target hardware, status of an ongoing operation, including a heartbeat signal of the target hardware, result indicators of the finished operations, etc.

# 3.5 ARINC 664

ARINC 664 is a seven part ARINC specification (see [13], [14], [15], [16], [17], [18], and [19]). It defines an Ethernet data network suitable for an aircraft installation. Each of the aforementioned documents describes some area, e.g. system concepts, Ethernet physical and data link layer, Internet-based protocols and services, etc.

Basically, the main goal of this standard is to set requirements and restrictions that have to be met in order for the standard commercial Ethernet networks and Internet protocols to be eligible for the use in aircrafts.

ARINC 664 standard is not a key standard for this thesis, therefore it is not described in greater detail here. However, AFDX network was mentioned in section 3.4 as a possible layer, upon which ARINC 615A standard can be implemented, hence at least a short description of AFDX follows.

Avionics Full-Duplex Switched Ethernet (AFDX) is a trademark of Airbus company. Airbus has it patented for safety-critical applications. AFDX network is able to provide deterministic quality of service (QoS) on a dedicated bandwidth.

There are two types of devices connected to an AFDX network. End systems and switches. AFDX implements the so called virtual links, which make an abstract layer and simulate a bus similar to the one defined by ARINC 429. Using virtual links, one source end system can create a unidirectional logical link to one or more destination end systems. Redundancy is used in the background, which means end systems actually communicate over multiple independent networks. In case of switch or link failure in one network, the connection shall not be interrupted.

# 3.6 ARINC 665

ARINC 665 is an ARINC report called Loadable Software Standards (see [5]). It defines the format of the loaded software. This definition includes the rules for part numbering, content, labeling, and formatting of loadable software parts (LSPs) and media set parts (MSPs). Subset of LSPs are loadable software airplane / aircraft parts (LSAPs). Compliance with the ARINC 665 standard assures, that software can be processed by standardized data loaders.

Each LSP should have exactly one part number (PN), which should be agreed upon by the aircraft manufacturer and the software supplier. Whenever a change is made to an LSP, PN should be changed as well. The PN format is defined as *MMMCC-SSSS-SSSS*, where (cited from [5], page 6):

- *MMM* is a unique, upper-case alphanumeric identifier called manufacturer's code, that is assigned to each software supplier

- CC are two check characters generated from the other characters in the PN

- SSSS-SSSS is a software supplier defined unique product identifier consisting of upper-case alphanumeric characters, except for alpha characters I, O, Q, and Z.

However, ARINC 615A compliant data loaders should not check the PN format in order to achieve higher backward compatibility and flexibility.

ARINC Industry Activities assigns manufacturer's code upon application. It also administers the already existing codes and a list of them can be found on ARINC Industry Activities website.

CC denotes 8 bit cyclic redundancy code (CRC) written as two hexadecimal digits. CRC is computed from the ASCII values of the rest of the PN characters.

An LSP consists of a header file and one or more data files. Furthermore, it can contain support files. Each file within an LSP should have a unique name with maximum length of 255 characters including an extension. The filename of the header file should start with the three character manufacturer's code and the rest should be unique for each LSP from this manufacturer. Characters that can cause problems on some platforms, like spaces, \*, /, etc., are restricted. Also, the only difference between two filenames cannot be in the use of uppercase and lowercase characters.

Each type of LSP file should have an extension. For example, header filename should end with .LUH, data filename should end with .LUP, etc. The full list of extensions for all file types can be found in [5], table 3.2.2-1 on page 28. Support files can have any user defined extension, as long as it does not conflict with the reserved ones.

The content of LSP header file is thoroughly described in [5], section 2.2.3.1 and its subsections on pages 9 to 20. For the data files and support files there are no expectations regarding their content or format. These types of files can optionally be compressed to save space and speed up the loading process, or they can be encrypted.

The standard also defines batch file part (BFP), which can be utilized to predefine a set of LSPs that should be loaded into one or more target hardware devices (positions).

MSPs in the context of ARINC 665 standard are the physical media, that are used to transport LSPs, and eventually BFPs. They also have PNs. PN should be agreed upon by the aircraft manufacturer and the software supplier. It should not be longer than 15 characters. The PN should uniquely identify the particular combination of physical media and the software content.

Each member of an MSP is identifiable by MSP's PN and the member sequence number, which should be from range of 1 to 255. Members of one MSP should use the same physical media, e.g. USB sticks, CDs, etc. LSP files can be distributed over more MSP members. However, individual files should never be split.

Each member of an MSP has a list of all contained LSPs stored in *LOADS.LUM* file, a list of all contained files stored in *FILES.LUM* file, and a list of all BFPs stored in *BATCHES.LUM* file. These files should be stored in the root directory of the MSP member. The full definition of the content and format of these files can be found in [5], section 3.2.3.1 and its subsections on pages 28 to 32, section 3.2.3.2 and its subsections on pages 32 to 37, and section 3.2.3.3 and its subsections on pages 37 to 40, respectively.

The standard also describes in detail the way MSPs should be labeled. Label should for example contain the MSP's PN, sequence number, content description, supplier identification, etc. The full description can be found in [5], section 3.3 and its subsections on pages 42 to 44.

# 3.7 ARINC 781

ARINC 781 is an ARINC characteristic called Mark 3 Aviation Satellite Communication Systems (see [20]). It sets forth the desired characteristics of satellite communication systems which are using Inmarsat satellites and operate in L-band (band from 1518 MHz

to 1559 MHz for reception and 1626.5 MHz to 1660.5 MHz and 1668 MHz to 1675 MHz for transmission).

The communication system consists of multiple parts, which are individually described in the standard. To simplify it, the system can be viewed as a satellite data unit (SDU), an antenna system, and an SDU configuration module (SCM). The standard broadly discusses the radio frequency (RF) parameters put onto the whole system and its individual parts (e.g. frequency ranges, limits for RF output power, power of intermodulation products, error vector magnitude, spurious emissions, etc.). Interfaces, both those provided by the SDU for cockpit and cabin services, and those for interconnection of the system parts, are also described, as well as the physical parameters, power supply, cooling, and many other parameters.

The standard also explains Inmarsat services, their types (Classic Aero, Swift 64, Swift-Broadband), parameters, etc. Services that should be provided by the SDU, for example aircraft communications addressing and reporting system (ACARS), are discussed, too.

There is also a brief mention about the data load. ARINC 781 states, that the SDU should be designed so that all embedded software components can be loaded through industry standards ARINC 615 and ARINC 615A data loaders. It should also be possible to download the owner requirements table (ORTs) from the SDU to a data loader. SDU software files should be compliant with ARINC 665 (taken from [20], pages 70 and 71).

# 4 ASPIRE 400

Aspire 400 is a satellite data unit (SDU) developed by Honeywell company. The target market for this unit consists of small and medium aircrafts. The purpose of this unit is to provide an aircraft with air-to-ground and ground-to-air connectivity. Basically, Aspire 400 can be viewed as a modem. Aspire 400 SDU is also a line replaceable unit (LRU, defined in section 3.2).

In this chapter, the internal structure of the SDU is described in section 4.1. This description is concerned with the structure that is important for the data load process. In section 4.2 and section 4.3, software configurations used on the two keys components of the unit are described. Possible data load scenarios tied with these configurations are described in chapter 5. The testing environment used in production of Aspire 400 SDUs is described in section 4.4.

# 4.1 SDU structure

Since Aspire 400 is currently an ongoing commercial project, the description of the SDU below goes only into detail necessary for the matter of this thesis. The full hardware structure of the components and their connections cannot be revealed, since these details could be used by Honeywell's competitors.

From the data load point of view, there are two important components in an SDU. Multiprocessor Card (MPC) and Dual Aeronautical BGAN Card (DABC, BGAN stands for Broadband Global Area Network). There is also an SDU Configuration Module (SCM), a separate component outside of the SDU box, which contains some customer specific data. These components are described below.

SDU provides multiple ways of connectivity, including ARINC 429 interface, RS-232 and RS-422 COM port serial interfaces, and Ethernet interface. These can be utilized in the data load process. Most connectors of an SDU are physically placed on its backplane in the ARINC 600 connector. Some of them are also accessible on the front panel.

Both MPC and DABC are connected to a so called backplane, which is another card within the SDU. Its main purpose is simply to provide interconnections between MPC and DABC and SDU's ARINC 600 connector.

MPC, DABC, and backplane card are also sometimes called shop replaceable units (SRUs). Like LRU, SRU is a term used in avionics. It denotes hardware on a lower level than LRU. While LRU can be quite easily replaced in the field, piece for piece, SRU usually has to be replaced in the LRU manufacturer's facility, where the LRU is disassembled in order to replace the SRU. Hence the name shop replaceable unit.

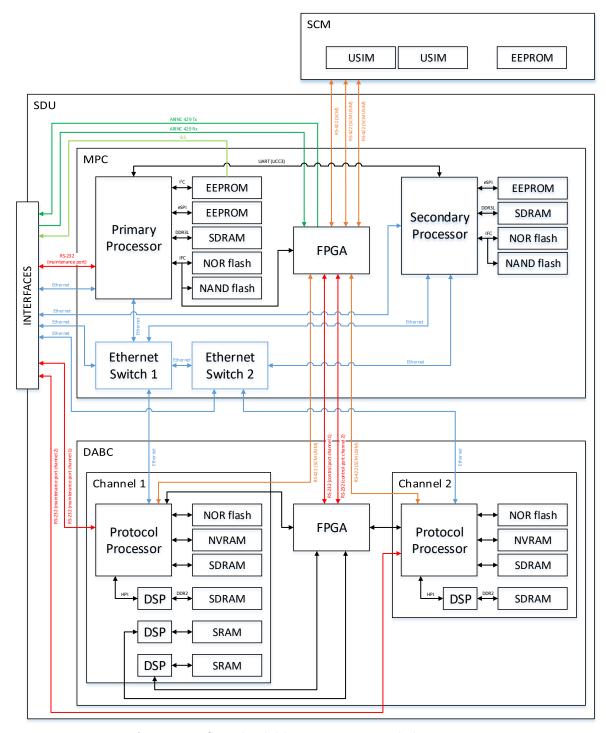

A simple visualization of the loadable components of an Aspire 400 SDU and their interconnections can be found in Figure 4.1. It shows a simplified structure of the unit, with emphasis on the information important for the data load.

Fig. 4.1: Aspire 400 SDU loadable components and their interconnections

# 4.1.1 MPC

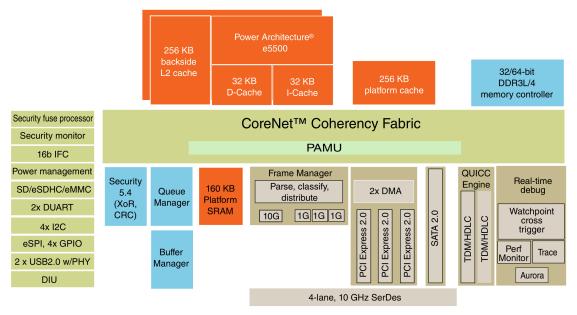

Main processor card (MPC) is the brain of Aspire 400 SDU. It has two processors that require data load. These processors are identical from the hardware point of view. They are both a system on chip with two 64 bit processor cores using Power Architecture

instruction set architecture. They provide high-performance data path acceleration and network and peripheral bus interfaces useful for aerospace applications. A block diagram of the system can be found in Figure 4.2. The diagram is taken from the processor's data sheet, but it cannot be cited in order to keep the processor model undisclosed.

Fig. 4.2: MPC processor block diagram

From the functional point of view, the processors have different tasks in the SDU. However, their individual domains are not important for this thesis and therefore they remain undisclosed. For the data load problematic, it is important to state that one of the processors, hereafter referred to as primary processor, is booted first during the boot up of the SDU and controls the other components, namely the other processor, hereafter referred to as secondary processor, and the DABC.

Each of MPC's processors has four external memories. Three non-volatile and one volatile. The non-volatile memories are one Micron 128 MB NOR flash, one Micron 1 GB NAND flash, and one Microchip Technology 64 KB EEPROM. The first two memories are connected to the processor via the Integrated Flash Controller (IFC) bus. This bus is 16 bit wide and clocked at 100 MHz. It provides a NOR flash controller, a NAND controller, and a General Purpose Chip Select Machine (GPCM) controller (see [21], slide 4). The EEPROM is connected via Enhanced Serial Peripheral Interface (eSPI) bus.

The volatile memory is a 1 GB DRAM error-correcting code (ECC) protected DDR3L SDRAM, namely two 512 MB Micron chips are used. The L in DDR3L stands for low-voltage (memory is operating at 1.35 V instead of standard 1.5 V). ECC protection detects and corrects all single-bit errors and detects all double-bit errors. The ECC is a 256 MB Micron chip, which is not user accessible. All memories are organized in a virtual address space addressed with 32 bits for each processor.

In a typical boot up scenario, when the power is turned on, the system starts execution from a non-volatile memory (e.g. EEPROM or NOR or NAND flash). After that, the code is copied from a persistent storage into RAM and execution continues from there (see [21], slide 3). Therefore the processor needs to be able to communicate with the non-volatile memory before any software configurations are made. In case of MPC, the boot up process is started from the EEPROM and NOR flash and the program data are copied to RAM from the NOR flash.

There is one more Microchip Technology 64 KB EEPROM, which is a part of the Standalone Identification System (SIS) interface. It is used to store the unit level configuration information. It is accessible both from the primary processor via an Inter-Integrated Circuit (I<sup>2</sup>C) bus, and externally using the SIS interface. This interface allows user to check the configuration stored in its EEPROM without the necessity to have the SDU powered on. The SIS interface is made up by 8 pins. The connector is a 9 pin D-Sub connector placed on the SDU's front panel. The SIS interface can only read out of the EEPROM. The primary processor has to be used in order to write data into it.

The primary processor provides an RS-232 port called MPC maintenance port and both processor are reachable via Ethernet interfaces, either directly or via Ethernet switches which are part of MPC as well. All these connectors are accessible on SDU's backplane (they are part of the ARINC 600 connector).

The primary processor and the secondary processor are interconnected via a serial link which is realized by universal asynchronous receiver / transmitter (UART) using UCC3 (Unified Communications Controllers) through the QUICC Engine (see subsection 4.2.4).

The Ethernet switches on MPC are made by Atheros. The direct Ethernet connections to MPC's processors are realized using PHY chips (circuitry implementing physical layer of the OSI model), namely serial gigabit media-independent interface (SGMII). The Ethernet connections via switches are either SGMII or reduced gigabit media-independent interface (RGMII). Both switches and both PHYs are controlled by the primary processor over MDC/MDIO serial bus. The active device is selected by a 1:4 multiplexer.

MPC also contains a Microsemi FPGA, which is controlled by the primary processor via the IFC bus. This FPGA, among other things, implements the ARINC A429 interface, and it also controls reset signals to other components in the SDU (the secondary processor and DABC).

Other important parts of MPC are three pin header JTAG connectors, one for each processor (16 pins) and one for the FPGA (10 pins). There are also another two 10 pin header connectors, one for each processor's EEPROM. These connectors are used for testing and data load, as described in more detail in chapter 5 and chapter 6.

# 4.1.2 DABC

Dual Aeronautical Broadband Global Area Network Card (DABC) is the modem part of Aspire 400 SDU. This component is connected to an antenna mounted on an aircraft and using this antenna serves as the transmitter and receiver of the radio frequency (RF) signals. Based on the type of antenna, an amplifier might be also used, or it can be part of the antenna itself.

DABC also provides processing of RF signals, which includes modulation and demodulation, encoding and decoding, implementation of protocol stacks for Inmarsat services, etc. Inmarsat's SwiftBroadband (SBB) network is used for communication. SBB is a global IP-based packet-switched network providing aircraft connectivity with speed up to 432 kbps per channel (see [22]). It uses Inmarsat satellites to operate.

DABC, as the word Dual in its name suggests, has two independent channels. Each one has its hardware and is loaded separately. More information about the data load of DABC can be found in chapter 8. DABC is sometimes also called channel card (CC), since its purpose is to provide RF communication channels.

From the hardware point of view, which is again kept at a level necessary for the data load process, DABC has one FPGA common for both channels, each channel has one general purpose processor, one channel has one DSP and the other channel has three DSPs.

The FPGA is made by Xilinx. Apart from other things, the so called control processor is implemented for each DABC's channel within this FPGA. Its main purpose is to select the application that is supposed to be started during DABC's boot up process. The control processor is commanded via an RS-232 control port. It is also connected to the other components, which can be commanded via the control port as well.

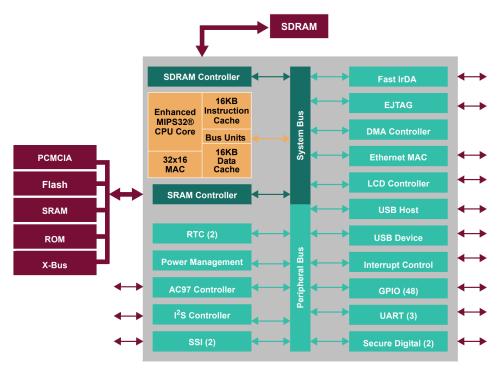

The general purpose processor is a high performance low power system on chip based on MIPS32 instruction set. In DABC, it is called a protocol processor, since its main purpose is to run applications processing Inmarsat protocols. A block diagram of the system can be found in Figure 4.3. Same as with the MPC processor, the diagram was taken from the processor's data sheet, but the document cannot be cited because it naturally contains the model name of the processor.

There are three memory chips connected to this processor. One non-volatile 32 MB Micron NOR flash connected via the SRAM controller, one volatile 32 MB Micron SDRAM connected via the SDRAM controller, and one 256 KB Cypress Semiconductor SRAM connected via the SRAM controller. The last memory is volatile by nature, but in DABC, a condenser is used to make the data in it persistent. The condenser should last at least one minute, but in reality, it can hold the data much longer. Anyway, the data are persistent through a restart of the card, therefore this memory can be viewed as a sort of NVRAM. The protocol processor is also connected to the RS-232 maintenance port and to the Ethernet port.

The DSPs are made by Texas Instruments. The one used on both channels has a 128 MB Micron DDR2 SDRAM. It is connected to the protocol processor via Host Port Interface (HPI) bus and to the FPGA via GPIO lines. HPI is a parallel port through which the protocol processor can directly access the memory space of the DSP, including memory-mapped peripherals (see [23]). Protocol processor acts as a master on the bus.

The other DSPs used only on the first channel are identical and both have a 256 KB Cypress Semiconductor SRAM, which is organized as 128K 16 bit words. These DSPs are connected only to the FPGA via GPIO lines.

Fig. 4.3: DABC processor block diagram

A 40 bit virtual address space is used to map all DABC components into it to simplify the access to them.

Like MPC, DABC also has JTAG lines which can be utilized for testing and data load. Unlike MPC, on DABC there is only one dedicated JTAG connector (for the RF part) and other lines (for the channel 1 and channel 2 protocol processors and for the FPGA) are part of DABC's backplane connector, i.e. defined pins of this connector are dedicated for this functionality.

#### 4.1.3 SCM

SDU configuration module (SCM) is a separate module containing an EEPROM memory in which some important unit-specific configuration data used by flight code are stored. It contains for example serial number of the unit, information about both hardware and software configuration and customer data. Customer data are stored in the so called owner requirements table (ORT).

SCM also contains slots for Universal Mobile Telecommunications Service (UMTS) Subscriber Identity Modules (USIM) cards, which are used by Inmarsat to connect to its Swift Broadband network. USIM cards are necessary for the DABC to be able to operate.

SCM is connected to an SDU via RS-422 serial interface and power is also provided by the SDU. The advantage of having SCM as a separate module is that it can stay in the aircraft while SDUs are swapped. When a new SDU is used, ORT does not need to be loaded again since it is part of the SCM, and USIMs can also remain untouched.

# 4.2 MPC Software Parts

In this section, software used on MPC is described. There are multiple possible software configurations of MPC consisting of a combination of the software parts described below. More information about these configurations can be found in chapter 5.

# 4.2.1 FPGA Configuration

A file with data for the MPC's FPGA is necessary to program it. Microsemi flash programmer allows usage of either PDB or STP file formats. The file contains data for the boundary scan test a the FPGA configuration.

# 4.2.2 RCW

MPC's processors use a mechanism called pre-boot loader (PBL). PBL is automatically executed when the processor is powered on and its main task is to load the reset configuration word (RCW), which is stored in processor's EEPROM. RCW is 512 bits long and contains encoded information used to initialize the RCW status registers. The information encoded within RCW sets for example clock speed, RAM attributes, etc.

#### 4.2.3 Miniboot

Miniboot is a simple executable code that verifies the checksum of U-Boot (see subsection 4.2.4). It is stored in processor's NOR flash and run after the processor is powered on and RCW is loaded.

Miniboot first tries to verify checksum of the primary U-Boot image and if it is correct, Miniboot hands execution over to this U-Boot image. If this checksum is not correct, Miniboot tries to verify checksum of the secondary U-Boot image. If this image is correct, Miniboot starts its execution. If not, the SDU halts.

#### 4.2.4 U-Boot

U-Boot, or Universal Boot Loader, is an open source project, which provides firmware for embedded systems. The core development is done by DENX Software Engineering company from Germany. The versions used in Aspire 400 project are customized at Honeywell. The purpose of U-Boot is to perform hardware specific initialization and testing (e.g. RAM test).

There are two main advantages of U-Boot. First is that it can boot up a system already loaded into the device's memory, and, unlike in most bootloaders, user can specify the addresses in memory used by the boot commands.

The second is it provides a command line interface via RS-232 port. This interface can be accessed when U-Boot startup process is interrupted by a keystroke during the prompted time period. The interface supports commands for writing to, or reading from the memory, modification of the environment variables, transferring files over the RS-232

serial interface (using for example YMODEM file transfer protocol), or Ethernet interface (using for example trivial file transfer protocol, i.e. TFTP), etc.

On MPC, there are two identical U-Boot images for each processor stored in its NOR flash. As already described in subsection 4.2.3, one image is primary and the other one is secondary. Integrity of an image is checked before it is started by computing its checksum. Normally, only primary image is used (unless it is corrupted).

However, one exception to this duplicity exists. The environment variables are stored in the so called U-Boot environment memory space in the NOR flash, and this space is unique. The environment variables are loaded upon U-Boot's startup and they contain values which determine the behavior of U-Boot. In case the U-Boot environment is found to be corrupted (again checked by a checksum), U-Boot sets all environment variables to default values. And in case the U-Boot image is found to be corrupted, this information is stored in the environment variables.

U-Boot also loads two microcodes (sometimes also spelled as  $\mu$ codes). Each controls behavior of a certain hardware block within the processor. First is FMan, or Frame Manager, which processes Ethernet frames to provide classification and intelligent distribution and queuing for incoming traffic. Second is QUICC Engine, which serves for high-performance multiprotocol processing, e.g. Unified Communications Controllers (UCC). Both microcodes are provided by NXP, both are stored twice in the processor's NOR flash and their checksums are checked by U-Boot.

#### 4.2.5 HBIT

Hardware built-in test (HBIT) is a software specifically designed to allow testing of all the components of an Aspire 400 SDU. The target of this testing is to make sure the hardware of the tested SDU is functioning correctly, i.e. all the components of the printed circuit boards and their interconnections are in place and are working as expected.

Basically, the purpose of HBIT is to provide an interface that allows setting or reading out variables. A typical test scenario is when a set of variables is set in a predefined way, and another set of variables is read out to see if the hardware reacts to the setup as expected. There are many different variables to cover all the test scenarios. There are discrete signals, analog signals, data sent over various buses, RF setups, etc.

HBIT is loaded onto MPC, but it also has the ability to control DABC in order to set it up for the RF test scenarios.

For some tests, the environment outside of the tested unit also needs to be set up. Most typically, voltages and currents are measured, so probes have to be set up correctly. Or some inputs and outputs need to be looped, temperature has to changed for the test, etc. This is not done by HBIT itself, but by the testing platform (see section 4.4).

HBIT also provides functionality called Continuous built-in test (CBIT). As the name suggests, CBIT is a version in which testing is continuous, i.e. the tested variables are read out with a defined frequency until the process is stopped. Compared to that, in HBIT, the

variables are read out on demand. The tested values that are read out can be compared programmatically, they can be logged, they can be visualized, etc.

# 4.2.6 Flight Code

Flight code is the full feature version of the software that is used on board of an aircraft. Prior to any regular in-flight usage, this software has acquire proper certification. It undergoes the so called qualification process, during which it is inspected and tested by all the interested aviation authorities, and, if it complies with all the requirements and passes the tests, it is certified.

In case of Aspire 400 SDU, more precisely the MPC, flight code is a Linux-based module system. Each module takes care of some specific functionality. It is basically a process. The so called message event service (MES) is implemented to provide an interprocess communication between the modules. MES also provides means for securing the communication, i.e. encoding and decoding the messages.

Flight code modules are distributed on MPC's processors. Each processor takes care of different parts of the SDU's functionality. But the functional domains of flight code are not important for the topic of this thesis, therefore they are not described further. Only the modules important for this thesis, e.g. data load controller (DLC), are described in greater detail in chapter 9.

Flight code is released in a form of flattened image tree (FIT). It is an image of the whole system, including all configurations. This image is part of the loadable package compliant with ARINC 665 standard. The standard in general was described in section 3.6 and for its application on Aspire 400 project see chapter 9.

# 4.3 DABC Software Parts

DABC is commanded by the MPC. Nevertheless, different configurations for DABC exist and the code is loaded separately. Moreover, as mentioned earlier, DABC has two separate channels, and each of them is loaded separately as well.

The DABC software is released in a form of image files (.img suffix). Based on the type of application, the file contains data for one or more of DABC's components. The application is usually loaded onto all DABC components it uses during one instance of the data load process. This ensures the software for individual components is compatible. But it is also possible to load individual components with a specific combination of software versions. This is especially useful for some extensive debugging, when user can create a customized software version for the component of interest and load just that one.

Multiple applications can coexist in DABC's non-volatile memory (protocol processor's NOR flash) at the same time. The active one is picked during the boot up using the so called loader program, which is described in the next subsection. Records about available applications are kept in a special table stored in the NOR flash as well. This so called

PDB table contains names and versions of applications, together with their checksums and addresses in the NOR flash.

Some environment variables can also be stored in protocol processor's NVRAM. Factory values are stored in the NOR flash and they are loaded from there to the NVRAM, where they can be modified. The reason for this approach is that the NOR flash always holds the factory data as a form of a backup and when modified, the change is done in the NVRAM, so no writes to NOR flash are necessary. This reduces the number of writes to this memory, which reduces its wear-off speed.

The list of DABC applications in this section is not exhaustive. Other types of DABC images, mainly for different testing purposes, also exist. However, these are not used during production testing and therefore they are not listed here.

A proprietary language called Binary Command Language (BCL) is used to command DABCs. It is used to communicate with DABC from any external device or component. A library for translation of BCL commands into binary and vice versa has to be available in order to use it. All of DABC's functionality is accessible using BCL commands. The commands can be sent either via control port or maintenance port (RS-232) or via Ethernet (TCP/IP stack).

Each BCL message has mandatory header and optional data payload based on the message type. The header contains information about sender (BCL address of the sending component) and recipient (BCL address of the target component). It has also information about the type of the message, its length, CRC, and other properties.

# 4.3.1 FPGA Configuration

Like on MPC, a file with data for the DABC's FPGA is necessary to program it. On DABC, Serial Vector Format (SVF) file is used. This file contains instructions that perform the boundary scan test a configure the FPGA into the desired state. SVF files are ASCII encoded.

# 4.3.2 Loader Program

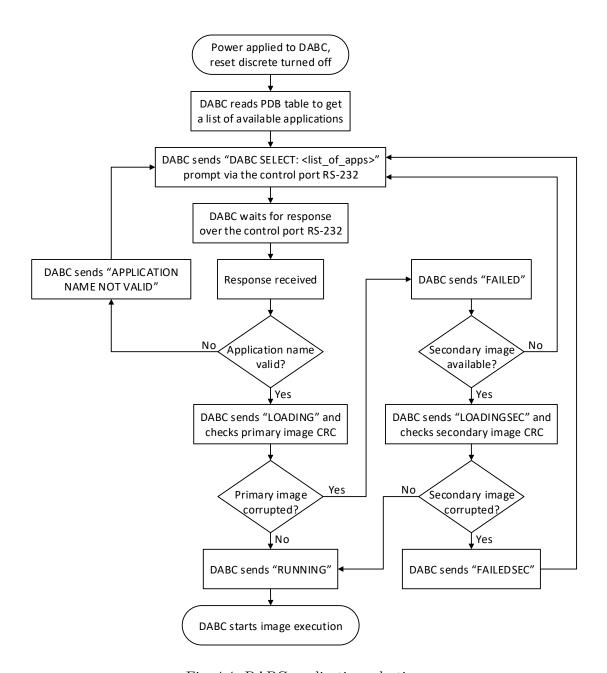

After power is applied to DABC and the reset signal is turned off, loader program is initiated. This program reads the PDB table with information about all available applications mentioned above from the NOR flash and presents a list of available applications via the control processor interface (control port RS-232). Selection is done using ASCII encoding, i.e. application is selected by typing its name over the control port, terminated with a carriage return character. When a correct application name is supplied, the loader program copies the application from the NOR flash into RAM and hands over the control to the application.

All applications can actually be twice in the NOR flash. This is for security reasons. When application is loaded to DABC (written to its NOR flash) a copy of it can be made. It is used in case the primary image gets corrupted. Before the loader program copies the application into RAM, it computes CRC of the image it is about to copy to check

the image is correct. If the CRC does not check out with the one stored in the PDB table, user is informed about the error, but if the secondary image is available, the loader program tries to copy the application from there (it performs the CRC check again for the secondary image). Secondary image is only used if the primary is either not present or its CRC is not correct. A flow chart of the loader program functionality is shown in Figure 4.4.

Fig. 4.4: DABC application selection

#### 4.3.3 EBOOT

Emergency boot (EBOOT) is an application which allows overwriting DABC's NOR flash using BCL. Hence data load can be performed when this application is running on the channel that is about to be loaded. EBOOT is using only the protocol processor to run.

EBOOT also supports duplication of the other applications' images in the channel's NOR flash, which was mentioned in the previous subsection. When the BCL command to perform the duplication is received by the protocol processor, EBOOT tries to copy the other images present in the NOR flash from their primary position to their backup position. It first checks to see if the duplicates are already present and are exactly the same as the primary images. If so, no duplication is performed, both to speed up the process, and to omit unnecessary writes to the NOR flash. If not, EBOOT either performs the duplication or returns an error message when something goes wrong, for example if there is not enough space for the duplicate in its designated area in the NOR flash. There is also a BCL command that performs the opposite action, i.e. wipes the duplicates out of the NOR flash. EBOOT does not duplicate itself and it is the sole application that is able to perform this duplication and / or wiping.

Also, in contrast with loader program, when an application is running (not only EBOOT, but any), the channel can be controlled not just via control port RS-232, but via maintenance port RS-232 and Ethernet port, too. Other than that, EBOOT does not support any of DABC's functionality.

### 4.3.4 IBIT

Initiated built-in test (IBIT) application is used for testing DABC in operational use. This means that IBIT implements all functionality required to control DABC's hardware. IBIT is used during the production testing to command DABC to transmit and / or receive data via its RF module. BCL commands are used to achieve this.

#### 4.3.5 SwiftBB

SwiftBB, or SwiftBroadband, abbreviated SBB, is the full feature flight code application used in an aircraft. It is designed to provide means of communication over Inmarsat's Broadband Global Area Network (BGAN). It handles the RF signals, implements all the necessary protocols, etc. In order to be able to use BGAN, the implementation of this application has to comply with SBB protocols defined by Inmarsat.

# 4.4 ATE

Automated test equipment (ATE) is an apparatus used for production testing of SDUs. The testing is as automated as possible to speed up the process. Ideally, an operator only plugs the unit under test (UUT) into the ATE and starts testing. All tests should be performed and evaluated automatically, including all necessary configurations of the

testing environment. The operator only needs to check the final status of the tested SDU to see if it has passed or failed, and if it has failed, the ATE should also give reasons of failure, so the SDU can be possibly fixed.

An ATE for Aspire 400 project should support testing of two SDUs simultaneously. The testing process is coordinated by a computer that is part of an ATE. This computer is running Microsoft Windows operating system and a program called TestStand from National Instruments is used to run and evaluate the test sequences.

TestStand has the ability to call various adapters and interfaces. Its advantage is that it can unify calls into various libraries, programming languages, etc. This layer is abstracted from ATE's operator, and he or she is presented only with quite simple and clear interface showing which test sequences have passed or failed. TestStand also creates a test report, can log the measured values into database, and more.

Other necessary tools are also installed on the ATE's computer. For example a TFTP server enabling an SDU in U-Boot command line mode to download data from it.

In the production process, ATE also serves as the data loader for the load of HBIT onto MPC and IBIT onto DABC in the beginning of testing, and for the first-time load of flight code after the testing is finished. U-Boot has to be already present on MPC, as well as EBOOT on DABC, when the SDU it tested via ATE, since ATE tests SDUs (i.e. tests at the box level), while these applications have to be loaded at the card level, as described in more detail in chapter 6.

# 5 DATA LOAD SCENARIOS

During its lifetime, SDU has to go through multiple software configurations. First, when an SDU is produced, individual components are manufactured, i.e. printed circuit boards (PCBs) are made and assembled. Then some initial tests are performed on these components, for example automated optical inspection (AOI), automated X-ray inspection (AXI), in-circuit test (ICT), boundary scan, etc. At this time, the components are blank, therefore it is necessary to load some software onto them in order to use them. The software has multiple layers, starting with bootloaders at the lowest level. There can be more, building up on each other and extending the provided functionality. On top of bootloader, there is usually some operating system and at the top level, there are the final applications.

In production, the low level software is usually loaded by the component manufacturer. During development, when changes even to the low level software might be required, or the software might get corrupted by improper work with memory, it can be sometimes necessary to flash the component at Honeywell, too. But in most cases, the software at the lowest level is loaded once onto a blank component and does not need to be changed further.

Once the individual components are loaded with at least the low level software, the unit could be theoretically assembled and shipped for SDU level production testing. But in order to make sure the components work correctly prior to the SDU assembly, software designed specifically for testing of all required features is loaded onto them and functional testing at the card level is performed. This testing software is HBIT for MPC and IBIT for DABC (these software parts were described in subsection 4.2.5 and subsection 4.3.4, respectively). Only after both MPC and DABC pass, SDU is assembled and the testing process goes further.

The SDU level production testing is performed at Honeywell and uses HBIT and IBIT as well. It can happen that versions of these software parts used during the card level testing are the same as versions required for the SDU level testing. In such case, testing can proceed right ahead. However, it is more likely that the card manufacturer is provided with a different version of HBIT and / or IBIT by Honeywell, and it is therefore necessary to load these software parts once again.